Contents lists available at ScienceDirect

journal homepage: www.elsevier.com/locate/sse

# Compact I-V model for back-gated and double-gated TMD FETs

Ahmed Mounir<sup>a,\*</sup>, Benjamin Iñiguez<sup>a</sup>, François Lime<sup>a</sup>, Alexander Kloes<sup>b</sup>, Theresia Knobloch<sup>c</sup>, Tibor Grasser<sup>c</sup>

<sup>a</sup> Rovira I Virgili University, Tarragona, Spain

<sup>b</sup> University of Applied Sciences, Giessen, Germany

<sup>c</sup> TU Wien, Vienna, Austria

#### ARTICLE INFO

The review of this paper was arranged by Sorin Cristoloveanu

Keywords: 2D FETs MoS2 FETs Unified charge control model DC compact model

## 1. Introduction

In an effort to overcome the limitations of silicon-based CMOS devices in delivering the desired performance for Very Large-Scale Integration (VLSI) circuits, there has been increasing interest in using 2D materials as the conducting channel in Field Effect Transistors (FETs) [1]. This area of research is gaining momentum as a potential alternative to traditional silicon-based technologies. The ultra-thin nature of 2D materials is making it possible to achieve the ultimate scalability in FETs, resulting in enhanced gate electrostatic control over the channel and reduced parasitic effects when compared to 3D gate structures. Additionally, 2D materials show potential for use in stacked nanosheet transistor architecture [2]. Initially, research on 2D materials was focused on graphene, which possess exceptional electronic and optical properties [3]. However, due to its lack of a bandgap, its use in electronic circuits, particularly in digital electronics, is limited [4]. As an alternative, the research community began to explore other kinds of 2D materials, specifically Transition Metal Dichalcogenides (TMDs), which can be present in nature as insulators, semiconductors, metals, and even superconductors [5]. Compared to graphene, TMDs have gained more attention due to their relatively large bandgap, making them more suitable to be used in future logic electronics. MoS2 is the most extensively studied TMD, with high-performance MoS<sub>2</sub> FETs being reported in literature [6-8].

#### ABSTRACT

A physics-based analytical DC compact model for double and single gate TMD FETs is presented. The model is developed by calculating the charge density inside the 2D layer which is expressed in terms of the Lambert W function that recently has become the standard in SPICE simulators. The current is then calculated in terms of the charge densities at the drain and source ends of the channel. We validate our model against measurement data for different device structures. A superlinear current increase above certain gate voltage has been observed in some  $MoS_2$  FET devices, where we present a new mobility model to account for the observed phenomena. Despite the simplicity of the model, it shows very good agreement with the experimental data.

For any new device technology to be used in circuit design and simulation, compact models describing the I-V and C-V characteristics of the device need to be developed and made available to the designers. Those models work as a bridge between foundry and circuit designers. Those models will not only enable the design and simulation of circuits, but also will help interpreting experimental results. Several compact models regarding 2D FETs have been developed [9–14].

The focus of this paper is the development of a DC compact model for double and single back-gated TMD FETs. Our model utilizes a unified charge control model that stems from the formulation presented in [15]. In contrast to [15], we introduce an approximate explicit equation for the channel charge, which is expressed using a Lambert W function that is widely established in circuit simulators. Furthermore, the current is determined based on the charge densities at the source and drain. Our model is presented in the form of explicit closed equations that can be easily integrated into circuit simulators. Our model has been validated against measurement data, and we have observed a good agreement between the two, except for one kind of device technology, where a superlinear current increase was experimentally observed above a certain gate voltage. As a result, we introduced a new mobility model to account for the observed phenomena. This phenomenon might be related to the filling of traps. More details on the latter model can be found in [16]. It is worth noting that larger gate voltage sweeps were applied for this technology that we observe the superlinear current

\* Corresponding author. E-mail address: ahmed.mounir@urv.cat (A. Mounir).

https://doi.org/10.1016/j.sse.2023.108702

Available online 28 June 2023

0038-1101/© 2023 The Author(s). Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

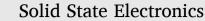

Fig. 1. 2D schematic structure for 2D TMD FETs. (a) Device 1 is a double gated monolayer  $MoS_2$  FET [15]. (b) Device 2 is a double gated monolayer  $WSe_2$  FET [17]. (c) Device 3 is single back-gated multilayer  $MoS_2$  FET [18]. (d) Device 4 is single back-gated monolayer FET [19].

Table 1

Input Parameters for the 2D FET model.

| Parameter                            | Symbol         | Device (1)               | Device (2)              | Device (3)               | Device (4)               |

|--------------------------------------|----------------|--------------------------|-------------------------|--------------------------|--------------------------|

| Channel Material                     |                | MoS <sub>2</sub>         | WSe <sub>2</sub>        | MoS <sub>2</sub>         | MoS <sub>2</sub>         |

| Length                               | L              | 150 nm                   | 9.4 μm                  | 500 nm                   | 4 µm                     |

| Width                                | W              | 10 µm                    | 10 µm                   | 10 µm                    | 10 µm                    |

| Top Oxide Dielectric Permittivity    | €t             | 9                        | 12.5                    | _                        |                          |

| Bottom Oxide Dielectric Permittivity | € <sub>b</sub> | 3.9                      | 3.9                     | 3.9                      | 3.9                      |

| Top Oxide thickness                  | t              | 10 nm                    | 17.5 nm                 | -                        | 15 nm                    |

| Bottom Oxide thickness               | t <sub>b</sub> | 285 nm                   | 270 nm                  | 90 nm                    | 25 nm                    |

| Mobility                             | μ              | 21.2 cm <sup>2</sup> /Vs | 235 cm <sup>2</sup> /Vs | 21.2 cm <sup>2</sup> /Vs | 19.1 cm <sup>2</sup> /Vs |

| Charge correction parameter          | α              | 2.4 @Vds = 0.1 V         | 1                       | 55                       | 18                       |

|                                      |                | 2.8 @Vds = 1 V           |                         |                          |                          |

| Charge correction parameter          | β              | 0.55 @Vds = 0.1 V        | 0.35 @Vds = -0.05 V     | 27                       | 9                        |

|                                      | ,              | 0.62 @Vds = 1 V          | 0.44 @Vds = -1V         |                          |                          |

| Mobility enhancement parameter       | М              | _                        | _                       | _                        | 0.8113                   |

| Mobility enhancement parameter       | $V_{ m A}$     | _                        | -                       | _                        | 7.48                     |

| Mobility enhancement parameter       | γ              | _                        | -                       | _                        | 0.5                      |

increase. On the other hand, the other technologies were measured over a smaller gate voltage range and that could be the reason why this phenomenon was not observed.

# 2. Model development

We begin the development of our physics-based compact model by modeling the device electrostatics. Our approach draws heavily on the findings of [15], which describes the electrostatics using the following equation.

$$Q_{\rm net} + Q_{\rm it} = -C_t \left( V_{\rm g} - V_{\rm g0} - V(x) + V_{\rm c}(x) \right) - C_b (V_{\rm b} - V_{\rm b0} - V(x) + V_{\rm c}(x))$$

(1)

here  $Q_{\text{net}}$  is the total mobile charge density,  $Q_{\text{it}}$  is the interface trap charge density,  $C_t$  ( $C_b$ ) are the top (bottom) oxide capacitances per unit area  $C_t = \frac{e_0 e_t}{L}$  ( $C_b = \frac{e_0 e_b}{L}$ ) and  $V_g - V_{g0}$  ( $V_b - V_{b0}$ ) are the top (bottom)

$$Q_{\rm net} = -qn(x) = -C_{\rm dq}V_{\rm th} \ln\left(1 + e^{\frac{-V_{\rm c}(x)}{V_{\rm th}}}\right)$$

(2)

where  $C_{dq} = q^2 D_0$  is defined as the degenerated-quantum capacitance and  $D_0$  is the density of states and defined as follows,

$$D_0 = g_{\rm K} \left( \frac{m^{\rm K}}{2\pi\hbar^2} \right) + g_{\rm Q} \left( \frac{m^{\rm Q}}{2\pi\hbar^2} \right) \exp\left( -\frac{\Delta E_2}{K_{\rm B}T} \right) \tag{3}$$

here  $g_K$ ,  $g_Q$  are the degeneracy factors,  $m^K$ ,  $m^Q$  are the conduction band effective masses for the K and Q band valley and  $\Delta E_2$  is the energy separation between K and Q valleys. By rearranging (2), we get,

$$V_{\rm c}(x) = -V_{\rm th} \ln\left(exp\left(-\frac{Q_{\rm net}}{C_{\rm dq}V_{\rm th}}\right) - 1\right)$$

(4)

Combining (4) and (1), we obtain the uniform charge control model (UCCM) that is expressed as follows,

$$Q_{\rm net} - C_{\rm tb} V_{\rm th} \ln\left(exp\left(-\frac{Q_{\rm net}}{C_{\rm dq} V_{\rm th}}\right) - 1\right) = -C_{\rm t} \left(V_{\rm g} - V_{\rm g0} - V(x)\right) - C_{\rm b} \left(V_{\rm b} - V_{\rm b0} - V(x)\right)$$

(5)

overdrive voltages, where  $V_{g0}$  ( $V_{b0}$ ) takes into consideration the work function difference and any possible additional charges resulting from impurities or doping. In MoS<sub>2</sub> FET devices, the interface trap charge density  $Q_{it}$  has a significant role in the transistor behavior. However, as an initial approximation in developing our compact model, we disregard the dependence of  $Q_{it}$  on the gate voltage. Instead, we treat  $Q_{it}$  as a constant value that impacts both the threshold voltage  $V_{TH}$  and the subthreshold slope *SS*. V(x) is the quasi-Fermi level along the channel, where  $V(x = 0) = V_s$  (source voltage) and  $V(x = L) = V_D$  (drain voltage).  $V_c(x)$  is the shift of the quasi-Fermi level with respect to the conduction band. The overall charge density can be also expressed as follows,

with  $C_{tb} = C_t + C_b$ .

Although Equation (5) can be used to obtain the overall mobile charge density through numerical methods, such solutions may not be practical in compact modeling, given their high computational cost and unsuitability for efficient circuit simulations. As a result, we approximate the poly-logarithmic term  $\ln\left(exp\left(-\frac{Q_{\rm net}}{C_{\rm dq}V_{\rm h}}\right)-1\right)$  to formulate our core model.

Using a two terms Taylor's expansion, we can rewrite the UCCM as follows,

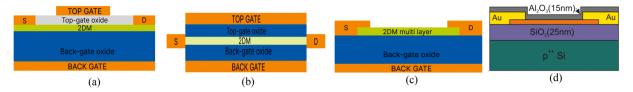

Fig. 2. Validation of the 2D FET model against experimental data for Device 1. (a) Linear transfer characteristics  $(I_D - V_{gs})$  at  $V_{ds} = 0.1$ , 1 V. (b) Transfer characteristics on the logarithmic scale.

$$Q_{\rm net}(x) - C_{\rm tb}V_{\rm th}\ln\left(-\frac{Q_{\rm net}(x)}{C_{\rm dq}V_{\rm th}}\right) = -C_{\rm t}\left(V_{\rm g} - V_{\rm g0} - V(x)\right) - C_{\rm b}(V_{\rm b} - V_{\rm b0} - V(x))$$

(6)

The mobile charge density throughout the semiconductor can be obtained by solving (6) analytically. To achieve that, we reformulate (6) in the form where the Lambert W function  $(\omega \exp(\omega) = z)$  can be applied. We do so by dividing both sides by  $C_{tb}V_{th}$  then exponentiate both sides. This allows us to rewrite (6) as follows,

$$\frac{\mathrm{d}Q}{C_{tb}V_{th}} - \frac{\mathrm{d}Q}{Q} = \frac{C_t \mathrm{d}V + C_b \mathrm{d}V}{C_{tb}V_{th}} \tag{11}$$

$$\frac{\mathrm{d}Q}{C_{tb}V_{th}} - \frac{\mathrm{d}Q}{Q} = \frac{C_{tb}\mathrm{d}V}{C_{tb}V_{th}} \tag{12}$$

$$\left(-\frac{Q_{net}(x)}{C_{tb}V_{th}}\right) \times \exp\left(-\frac{Q_{net}(x)}{C_{tb}V_{th}}\right) = \frac{C_{dq}}{C_{tb}} \exp\left(\frac{C_t\left(V_g - V_{g0} - V(x)\right) + C_b\left(V_b - V_{b0} - V(x)\right)}{C_{tb}V_{th}}\right)$$

(7)

Consequently, we can represent the total mobile charge density inside the semiconductor in terms of Lambert W function after introducing two fitting parameters  $\alpha$  and  $\beta$  as,

$$Q_{net}(x) = -\beta C_{tb} V_{th} W \left[ \frac{C_{dq}}{C_{tb}} exp\left( \frac{C_t (V_g - V_{g0} - V(x)) + C_b (V_b - V_{b0} - V(x))}{\alpha C_{tb} V_{th}} \right) \right]$$

(8)

To calculate the current, we need to calculate the charge densities at the source and drain ends. The current equation can be expressed as,

$$I_{\rm DS} = \frac{W\mu}{L} \int_0^{V_{\rm DS}} \mathcal{Q}(V) . \mathrm{d}V \tag{9}$$

Using equation (6), we can rewrite dV in terms of dQ as follows,

$$\frac{Q_{\text{net}}(x)}{C_{\text{tb}}V_{\text{th}}} - \ln\left(-\frac{Q_{\text{net}}(x)}{C_{\text{dq}}V_{\text{th}}}\right) = \frac{-C_t \left(V_g - V_{g0} - V(x)\right) - C_b \left(V_b - V_{b0} - V(x)\right)}{C_{tb}V_{th}}$$

(10)

$$dV = \frac{dQ}{C_{\rm tb}} - V_{\rm th} \frac{dQ}{Q}$$

(13)

Therefore, (9) can be written as follows,

$$I_{\rm DS} = \frac{W\mu}{L} \int_{Q_{\rm S}}^{Q_{\rm D}} Q(V) \left[ \frac{\mathrm{d}Q}{C_{\rm tb}} - V_{\rm th} \frac{\mathrm{d}Q}{Q} \right]$$

(14)

Integrating (14) results in,

$$I_{\rm DS} = \frac{W\mu}{L} \left[ \frac{Q_{\rm D}^2 - Q_{\rm S}^2}{2C_{\rm tb}} - V_{\rm th} (Q_{\rm D} - Q_{\rm S}) \right]$$

(15)

where  $Q_D$  and  $Q_S$  can be found by substituting  $V_D = V_{DS}$  and  $V_S = 0$ , respectively, in the charge equation, Equation (8). For the device technology with the super linear current increased observed, we have taken a three terms Taylor's expansion for the exponential term in (5), which is then used to develop the current equation, as derived in [16] after adjusting the model to a single back-gated structure. Hence, in this case the expression for the current is,

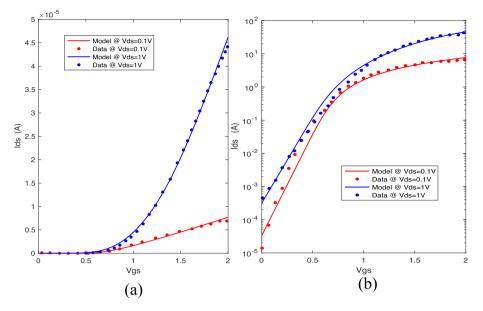

Fig. 3. Validation of the 2D FET model against experimental data for Device 2. (a) Linear transfer characteristics ( $I_D - V_{gs}$ ) at  $V_{ds} = -0.05$ , -1 V. (b) Transfer characteristics on the logarithmic scale.

$$I_{\rm DS} = \frac{W\mu}{L} M \left( \frac{V_{\rm b}}{V_{\rm A}} + 1 \right)^{\gamma} \left[ \frac{Q_{\rm D}^2 - Q_{\rm S}^2}{2C_{\rm b}} - 2V_{\rm th} (Q_{\rm D} - Q_{\rm S}) - 2C_{dq} V_{th}^2 \ln \left( \frac{Q_{\rm D} - 2C_{dq} V_{th}}{Q_{\rm S} - 2C_{dq} V_{th}} \right) \right]$$

(16)

## 3. Results and discussion

We validate our model against measurement data for four different device structures. Device 1 is a double gate structure that is composed of a single layer n-type  $MoS_2$ , which was grown using chemical vapor deposition (CVD), and then transferred onto a 285 nm intrinsic Si/SiO<sub>2</sub> wafer [15]. Device 2 is a double gate structure that was reported in [17], which consists of a p-type monoatomic channel of WSe<sub>2</sub>. It is placed on

top of 270 nm of SiO<sub>2</sub>, which serves as an insulator and separates it from a doped-Si back-gate. Additionally, the channel is covered with 17.5 nm of ZrO<sub>2</sub>, which acts as a barrier for a top Pd gate. Device 3 is a single back-gate structure with multilayer MoS<sub>2</sub> as a channel grown on 90 nm SiO<sub>2</sub> [18]. Device 4 is a single back-gate structure using a monolayer MoS<sub>2</sub> which was grown on SiO<sub>2</sub> (25 nm)/p++-Si substrates via chemical vapor deposition (CVD) at 850 °C [19]. Fig. 1 shows the cross section for the devices used for validation. Table 1 shows the parameters used for

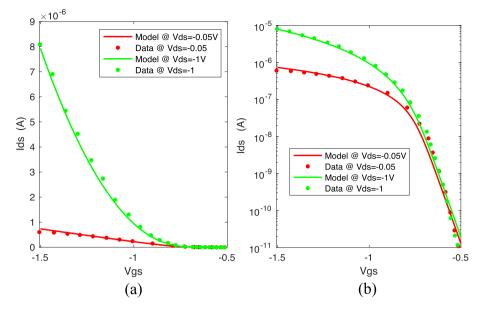

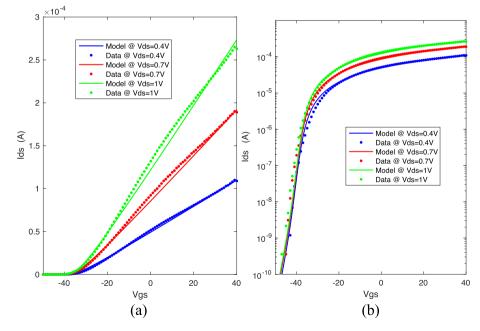

Fig. 4. Validation of the 2D FET model against experimental data for Device 3. a) Linear transfer characteristics  $(I_D - V_{gs})$  at  $V_{ds} = 0.4, 0.7, 1 V. b$ ) Transfer characteristics on the logarithmic scale.

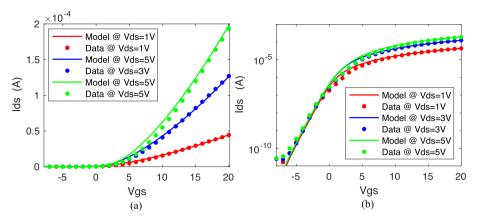

**Fig. 5.** Validation of the 2D FET model against experimental data for a single back gated structure Device 4. (a) Linear Transfer characteristics  $(I_D - Vgs)$  for Vds = 1 V, 3 V, 5 V for an encapsulated device at T = 165 °C. (b) Transfer characteristics on the logarithm scale for an encapsulated device at T = 165 °C.

each device. As mentioned before, Device 1:3 have less gate voltage sweep than Device 4, where the superlinear current increase has been observed.

Figs. 2–5 shows the validation for our model against measurement data for different device structures. The fitting was carried out to the best fit, where  $\alpha$  represents the ideality factor of the subthreshold slope which considers the interface trap densities and  $\beta$  is a fitting parameter that corrects the back gate capacitance. In Figs. 2 and 3 where the model fits Device 1 and 2,  $\alpha$  has lower values compared to Device 3 and 4 indicating lower values of interface state densities. Regarding Device 4, we needed to modify the mobility parameter to account for the superlinear current increase. As mentioned above this phenomenon might be related to the trap filling, which takes place above certain gate voltage. After the traps are filled, the excess carrier generation is now contributing to the current conduction resulting to a higher current value than expected.

### 4. Conclusion

We have presented a unified charge control model for double and single back-gated TMD FETs. The charge is expressed in terms of the Lambert W function. Subsequently, we compute the current by using the charge densities located at the source and drain terminals of the channel. One of the measured devices have much higher gate voltage sweep for the transfer characteristics, where we have observed a superlinear current increase in which we modified the mobility parameter to account for this phenomenon. Despite the simplicity of our model, it shows very good agreement with the experimental results and is expressed in an explicit closed form equation which is preferred for the incorporation into circuit simulators.

## **Declaration of Competing Interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

## Data availability

No data was used for the research described in the article.

### References

Sebastian A, Pendurthi R, Choudhury TH, Redwing JM, Das S. Benchmarking monolayer MoS<sub>2</sub> and WS<sub>2</sub> field-effect transistors. Nat Commun 2021;12(1):693. https://doi.org/10.1038/s41467-020-20732-w.

- [2] K. P. O'Brien et al., Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering, in 2021 IEEE International Electron Devices Meeting (IEDM), 2021, pp. 7.1.1-7.1.4. doi: 10.1109/IEDM19574.2021.9720651.

- [3] Wang J, Ma F, Liang W, Sun M. Electrical properties and applications of graphene, hexagonal boron nitride (h-BN), and graphene/h-BN heterostructures. Mater. Today Phys. 2017;2:6–34. https://doi.org/10.1016/j.mtphys.2017.07.001.

- [4] Das S, Robinson JA, Dubey M, Terrones H, Terrones M. Beyond graphene: progress in novel two-dimensional materials and van der Waals solids. Annu Rev Mater Res 2015;45(1):1–27. https://doi.org/10.1146/annurev-matsci-070214-021034.

- [5] Bhimanapati GR, Lin Z, Meunier V, Jung Y, Cha J, Das S, et al. Recent advances in two-dimensional materials beyond graphene. ACS Nano 2015;9(12):11509–39.

- [6] English CD, Shine G, Dorgan VE, Saraswat KC, Pop E. Improved contacts to MoS<sub>2</sub> transistors by ultra-high vacuum metal deposition. Nano Lett 2016;16(6):3824–30. https://doi.org/10.1021/acs.nanolett.6b01309.

- [7] Q. Smets et al., Ultra-scaled MOCVD MoS<sub>2</sub> MOSFETs with 42nm contact pitch and 250μA/μm drain current, in 2019 IEEE International Electron Devices Meeting (IEDM), 2019, pp. 23.2.1-23.2.4. doi: 10.1109/IEDM19573.2019.8993650.

- [8] Nourbakhsh A, et al. MoS<sub>2</sub> field-effect transistor with sub-10 nm channel length. Nano Lett 2016;16(12):7798–806.

- [9] Cao W, Kang J, Liu W, Banerjee K. A compact current-voltage model for 2D semiconductor based field-effect transistors considering interface traps, mobility degradation, and inefficient doping effect. IEEE Trans Electron Devices 2014;61 (12):4282–90. https://doi.org/10.1109/TED.2014.2365028.

- [10] Taur Y, Wu J, Min J. A short-channel I-V model for 2-D MOSFETs. IEEE Trans Electron Devices 2016;63(6):2550–5. https://doi.org/10.1109/ TED.2016.2547949.

- [11] S. V Suryavanshi, E. Pop, S2DS: Physics-based compact model for circuit simulation of two-dimensional semiconductor devices including non-idealities, *J Appl Phys*, 120 (22), p. 224503, 2016, doi: 10.1063/1.4971404.

- [12] Rahman E, Shadman A, Ahmed I, Khan SUZ, Khosru QDM. A physically based compact I-V model for monolayer TMDC channel MOSFET and DMFET biosensor. Nanotechnology 2018;29(23):235203. https://doi.org/10.1088/1361-6528/ aab5ac.

- [13] Yadav C, Rastogi P, Zimmer T, Chauhan YS. Charge-based modeling of transition metal dichalcogenide transistors including ambipolar, trapping, and negative capacitance effects. IEEE Trans Electron Devices 2018;65(10):4202–8. https://doi. org/10.1109/TED.2018.2855109.

- [14] L. Wang et al., A surface potential based compact model for two-dimensional field effect transistors with disorders induced transition behaviors, *J Appl Phys*, 124 (3), p. 034302, 2018, doi: 10.1063/1.5040908.

- [15] Pasadas F, Marin EG, Toral-Lopez A, Ruiz FG, Godoy A, Park S, et al. Large-signal model of 2DFETs: compact modeling of terminal charges and intrinsic capacitances. NPJ 2D Mater Appl 2019;3(1).

- [16] A. 'Mounir, B. 'Iñiguez, F. 'Lime, A. 'Kloes, T. 'Knobloch, and T. 'Grasser, Unified Charge Control Model for Back-Gated 2D Field Effect Transistors, submitted to IEEE Transaction on Electron Devices.

- [17] Fang H, Chuang S, Chang TC, Takei K, Takahashi T, Javey A. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett 2012;12(7): 3788–92. https://doi.org/10.1021/nl301702r.

- [18] Illarionov YY, Rzepa G, Waltl M, Knobloch T, Grill A, Furchi MM, et al. The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors. 2d Mater 2016;3(3):035004.

- [19] Y. Y. Illarionov et al., Anomalous Instabilities in CVD-MoS<sub>2</sub> FETs Suppressed by High-Quality Al<sub>2</sub>O<sub>3</sub> Encapsulation, in Proceedings of the Device Research Conference (DRC), 2020, pp. 150–151.