DISSERTATION

## On the Electrical Stability of 2D Material-Based Field-Effect Transistors

zur Erlangung des akademischen Grades

Doktorin der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

THERESIA KNOBLOCH

Matrikelnummer 1125050

Betreut von: UNIV.PROF. DIPL.-ING. DR.TECHN. TIBOR GRASSER Unter Mitwirkung von: MSC PHD DR.TECHN. YURY YU. ILLARIONOV

Wien, im Dezember 2021

## Abstract

Over the past decades, the continued scaling of transistors has reduced the energy consumption for every switching event and has increased the computational power of integrated circuits. However, nowadays, state-of-the-art silicon technology is reaching its physical limits and two-dimensional (2D) materials hold the promise of continued scaling down to dimensions of a few nanometers. In contrast to silicon, 2D materials maintain sizable mobilities in atomically thin layers. Gate control is enhanced over such thin channels, thereby mitigating short-channel effects in ultrascaled devices. Therefore, the community has devoted considerable efforts to develop performant, competitive and reliable field-effect transistors (FETs) based on 2D semiconductors. While numerous 2D semiconductors have been explored as channel materials and tremendous progress was made regarding the contacts to 2D materials, the equally important challenge of finding suitable gate insulators has yet received little attention. This thesis addresses this challenge of identifying good gate insulators, which is inherently linked to the goal of achieving a stable and reliable operation of 2D transistors. At the moment, substantial threshold voltage drifts render 2D FETs electrically unstable. These drifts are caused mainly by charge trapping at border traps in the gate insulator. Here, this issue is investigated using comprehensive measurements of the hysteresis in the transfer characteristics and the bias temperature instability, combined with physical modeling of these phenomena based on the charge transfer to border traps. Further insights on charge trapping are gained in single defect studies on nanoscaled 2D FETs at cryogenic temperatures. Based on these observations, we suggest a stability-aware design strategy for 2D FETs which can improve their electrical stability and reliability. By choosing a suitable alignment of the conduction and valence band edges of the 2D semiconductor in relation to the defect bands in the gate insulator, the number of charge trapping events can be considerably reduced. Another essential requirement for suitable gate insulators is their scalability down to equivalent oxide thicknesses of below one nanometer. At the same time, these thin layers need to sufficiently block tunneling currents to ensure low standby power consumption. Here, a theoretical lower limit of the projected leakage currents is established by modeling the tunnel currents in the defect-free case. In this way, it is shown that the layered crystalline insulator hBN is unsuitable as a gate insulator for ultrascaled CMOS circuits.

Based on our insights, we conclude that the most promising candidates for gate insulators for 2D FETs are crystalline gate insulators which form van der Waals interfaces with semiconducting monolayers while providing medium-sized dielectric constants and large band gaps. Besides, the understanding of charge trapping processes in 2D FETs developed within this thesis can be used to design novel 2D nanoelectronic devices for promising applications.

## Kurzfassung

In den letzten Jahrzehnten hat die kontinuierliche Skalierung von Transistoren den Energieverbrauch für jeden Schaltvorgang reduziert und die Rechenleistung integrierter Schaltungen erhöht. Allerdings stößt die moderne Siliziumtechnologie heute an ihre physikalischen Grenzen und zweidimensionale (2D) Materialien versprechen eine weitere Verkleinerung bis hin zu Dimensionen von wenigen Nanometern. Im Gegensatz zu Silizium behalten 2D Materialien hohe Beweglichkeiten in atomar dünnen Schichten bei und die Gatekontrolle wird durch die Verwendung solch dünner Kanäle verbessert. Daher wurden erhebliche Anstrengungen unternommen um leistungsfähige und zuverlässige Feldeffekttransistoren (FETs) auf Basis von 2D Halbleitern zu entwickeln. Obwohl zahlreiche 2D Halbleiter erforscht wurden und große Fortschritte auf dem Gebiet der Kontakte zu 2D Materialien erzielt werden konnten, wurde bis jetzt der ebenso wichtigen Herausforderung, geeignte Gateisolatoren zu finden, noch wenig Aufmerksamkeit geschenkt. In dieser Arbeit widmen wir uns dieser Herausforderung, welche inhärent mit dem Ziel verbunden ist, 2D FETs stabil und zuverlässig zu betreiben. Derzeit sind 2D FETs aufgrund erheblicher Schwellspannungsverschiebungen elektrisch instabil. Diese Spannungsverschiebungen werden hauptsächlich durch Ladungseinfang an Grenzdefekten im Gateisolator verursacht. Dieses Problem untersuchen wir anhand umfassender Messungen der Hysterese in den Transferkennlinien und der Spannungs-Temperatur-Instabilität, unterstüzt durch die physikalische Modellierung dieser Phänomene. Basierend auf diesen Beobachtungen schlagen wir eine stabilitätsbasierte Designstrategie vor, die die elektrische Stabilität und Zuverlässigkeit von 2D FETs verbessern kann. Indem eine geeignete Ausrichtung der Leitungs- und Valenzbandkanten des 2D Halbleiters zu den Defektbändern im Gateisolator gewählt wird, kann die Anzahl der Ladungseinfänge stark reduziert werden. Eine weitere wesentliche Voraussetzung für geeignete Gateisolatoren ist ihre Skalierbarkeit bis hin zu äquivalenten Oxiddicken von unter einem Nanometer. Gleichzeitig müssen diese dünnen Schichten Tunnelströme ausreichend blockieren, um so einen geringen Stromverbrauch im Standbymodus zu gewährleisten. Hier wird durch die Modellierung der Tunnelströme für den idealen, defektfreien Fall eine theoretische Untergrenze für die zu erwartenden Leckströme ermittelt. Auf diese Weise wird gezeigt, dass der geschichtete kristalline Isolator hBN als Gateisolator für ultraskalierte CMOS-Schaltungen ungeeignet ist.

Basierend auf unseren Erkenntnissen kommen wir zu dem Schluss, dass die vielversprechendsten Kandidaten für Gateisolatoren von 2D FETs kristalline Materialien sind, die Vander-Waals-Grenzflächen mit halbleitenden Monolagen bilden und gleichzeitig mittlere Dielektrizitätskonstanten und große Bandlücken bieten. Außerdem kann das im Rahmen dieser Arbeit entwickelte Verständnis der Ladungseinfangprozesse in 2D FETs genutzt werden, um neuartige nanoelektronische Bauelemente zu entwickeln.

## Acknowledgements

This thesis would not have been possible and would not have reached this scientific level without the ample assistance and support of many people. Thus, I would like to express my deepest gratitude to all who have contributed. In the following, I give an incomplete list, knowing that there is not enough space to thank each and every one of you.

First, I want to express my gratitude to my supervisor *Prof. Tibor Grasser* for providing me with the opportunity to join his research group. Moreover, his dedication and enthusiasm for his research field have always been highly inspiring and motivating. In my opinion, he has mastered the art of leading his research group and the entire institute by setting a good example. On numerous occasions, I have benefited from his tireless efforts to promote collaborations around the world. Thank you, Tibor, for your advice in challenging situations and for everything I have learned from you in recent years.

During my studies, the university's administrative staff always did an excellent job and I would like to thank *Christoph Neuherz* for helping me to arrange my defense on short notice. Also, I am proud and thankful that *Prof. Georg Düsberg, Prof. Paul Hurley* and *Prof. Walter Weber* are on my examination committee.

Furthermore, I would like to thank *Yury Illarionov*, who worked as a postdoctoral researcher in our group during my doctorate. We have been working together on a highly exciting research topic for over five years. I was inspired by his passion for research, his diligence and his hard working attitude. In addition, his drive to measure tremendous amounts of data and his willingness to co-author numerous joint publications has contributed considerably to the results presented within this thesis.

Additionally, I would like to thank *Michael Waltl*, who developed the custom-built measurement equipment I used for most of my electrical characterization experiments. He was of great help whenever I encountered issues during the measurement process. Besides, I want to thank *Lado Filipovic*, with whom I enjoyed working on several public outreach activities and research projects. His encouraging words and kind advice were very valuable.

I also wish to thank *Prof. Siegfried Selberherr*, together with *Ewald Haslinger*, *Manfred Katterbauer* and *Petra Kamptner-Jonas* for fostering a professional, productive and enjoyable working environment at the **Institute for Microelectronics**. In this context, my special thanks go to *Diana Pop* for her good humor and her unwavering support. I would like to express my gratitude to *Markus Jech, Jakob Michl, Christian Schleich, Bernhard Stampfer, Konstantinos Tselios* and *Dominic Waldhör* for many insightful scientific discussions and for the feedback they provided when proof-reading my thesis. Moreover, I want to thank my colleagues, *Johann*

#### Acknowledgements

*Cervenka, Al-Moatasem El-Sayed, Alexander Grill, Markus Kampl, Gerhard Rzepa* and *Mischa Thesberg* for contributing their time and expertise to this work.

At the **Birck Nanotechnology Center at Purdue University, USA**, I am deeply grateful to *Prof. Joerg Appenzeller* for providing me with the opportunity to join his group as a visiting scholar during two consecutive summers. He granted me access to device fabrication equipment and provided precious advice. In addition, I want to thank *Prof. Zhihong Chen* for her helpful feedback during group meetings. Many thanks go to my colleagues, *John Daniel, Neil Dilley, Xiangkai Liu, Chun-Li Lo, Chin-Sheng Pang, Peng Wu, Feng Zhang, Suki Zhang* and *Ruiping Zhou*. Here, I want to acknowledge funding received from the Marietta Blau grant, the Marshall plan scholarship and the Christiana Hörbiger award that provided the required financial resources for these research visits.

*Prof. Mario Lanza* welcomed me for an extended research stay to his lab at **Soochow University, China**. I would like to thank him for this memorable experience and his kind guidance. I would also like to thank my colleagues, *Shaochuan Chen, Fei Hui, Lanlan Jiang, Xianhu Liang, Yuanyuan Shi, Xiaoxue Song, Marco Villena, Bingru Wang* and *Chao Wen*.

Furthermore, I would like to thank our close collaborators at the **Ioffe Institute, Russia**. In particular, I want to thank *Prof. Nikolai Sokolov* and *Prof. Mikhail Vexler* for their warm welcome during my visit and their valuable contributions to this work as part of our ongoing cooperation.

This thesis is built heavily on fruitful collaborations. In this context I would like to thank *Prof. Thomas Müller* from the **Photonics Institute** and my colleagues from his research group, *Marco Furchi, Lukas Mennel, Dmitry Polyushkin* and *Stefan Wachter*. In addition, I want to thank my colleagues at **AMO GmbH, Germany**, *Prof. Max Lemme, Prof. Daniel Neumaier, Burkay Uzlu* and *Zhenxing Wang*. Furthermore, my thanks go to *Fabian Ducry* and *Prof. Mathieu Luisier* from the **ETH Zürich, Switzerland**. I also would like to acknowledge the modeling support from *Oskar Baumgartner, Franz Schanovsky* and *Zlatan Stanojevic* at **Global TCAD Solutions**.

Last but not least, I would like to thank my friends, especially, *Nina, Alexandra, Nikoletta, Stefan* and *Saskia* for their invaluable companionship and support over all these years. With shared laughter and tears you always helped me to get back on my feet. My deepest thanks go to my family, *Anna, Angelika* and *Peter*, thank you for being there for me and always having my back. Finally, thank you, *Benjamin*. My gratitude to you goes beyond what words can express.

## Contents

| Ab | ostra                                   | ct                                                                                                                  | i                          |

|----|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------|

| Kı | ırzfa                                   | ssung                                                                                                               | iii                        |

| Ac | knov                                    | wledgements                                                                                                         | v                          |

| Ac | rony                                    | /ms                                                                                                                 | xi                         |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | FoductionField-Effect TransistorCMOS Logic Scaling2D Materials Promise Ultimate ThinnessMotivation and ScopeOutline | 1<br>2<br>4<br>6<br>8<br>9 |

| I  | Sta                                     | ate-of-the-Art                                                                                                      | 11                         |

| 2  | Trai                                    | nsistors based on 2D Materials                                                                                      | 13                         |

| 2  | 2.1                                     | Material Synthesis and Transfer Methods                                                                             | 13<br>14                   |

|    |                                         | 2.1.1 Chemical Vapor Deposition                                                                                     | 15                         |

|    |                                         | 2.1.2 Metal Organic Chemical Vapor Deposition                                                                       | 17                         |

|    |                                         | 2.1.3 Molecular Beam Epitaxy                                                                                        | 19                         |

|    |                                         | 2.1.4 Atomic Layer Deposition                                                                                       | 20                         |

|    |                                         | 2.1.5 Transfer Methods for Layered Materials                                                                        | 20                         |

|    | 2.2                                     | Device Fabrication                                                                                                  | 23                         |

|    |                                         | 2.2.1 Etching 2D Materials                                                                                          | 25                         |

|    |                                         | 2.2.2 Scaling the Channel Area in 2D Transistors                                                                    | 28                         |

|    | 2.3                                     | Contacts to 2D Transistors                                                                                          | 30                         |

|    |                                         | 1 5                                                                                                                 | 32                         |

|    |                                         | 2.3.2 Contact Gating and Scaling                                                                                    | 37                         |

| 3  | Cha                                     | aracterization and Modeling of Performance and Reliability                                                          | 39                         |

|    | 3.1                                     | Performance Analysis                                                                                                | 39                         |

|    |                                         | 3.1.1 Transfer Characteristics                                                                                      | 40                         |

|    |                                         | 3.1.2 Threshold Voltage                                                                                             | 42                         |

|    |                                         | 3.1.3 Mobility Evaluation                                                                                           | 44                         |

|    | 3.2                                     | Device Stability and Reliability                                                                                    | 46                         |

|   |      | 3.2.1        | Low Frequency Noise                                                                 | 46  |

|---|------|--------------|-------------------------------------------------------------------------------------|-----|

|   |      | 3.2.2        | Random Telegraph Noise                                                              | 48  |

|   |      | 3.2.3        | Bias Temperature Instability                                                        | 49  |

|   |      | 3.2.4        | Time-Dependent Defect Spectroscopy                                                  | 52  |

|   |      | 3.2.5        | Hot Carrier Degradation                                                             | 52  |

|   |      | 3.2.6        | Time-Dependent Dielectric Breakdown                                                 | 53  |

|   | 3.3  | Mode         | ling Transistors Based on 2D Materials                                              | 54  |

|   |      | 3.3.1        | Non-Equilibrium Green's Functions                                                   | 55  |

|   |      | 3.3.2        | Drift Diffusion Models                                                              | 57  |

|   |      | 3.3.3        | Compact Models                                                                      | 59  |

|   | 3.4  | Charg        | ge Transfer Models                                                                  | 62  |

|   |      | 3.4.1        | Shockley-Read-Hall Model                                                            | 62  |

|   |      | 3.4.2        | Non-Radiative Multi-Phonon Model                                                    | 65  |

| Π | In   | nprov        | ing Transistors Based on 2D Materials                                               | 71  |

| 4 | Suit | -<br>table G | ate Insulators for 2D Transistors                                                   | 73  |

|   | 4.1  | Scalin       | g Requirements                                                                      | 73  |

|   | 4.2  |              | cing Charge Trap Densities and Their Impact                                         |     |

|   |      |              | Interface Traps                                                                     |     |

|   |      |              | Border Traps                                                                        |     |

|   | 4.3  | Depos        | sition Technology for Gate Insulators                                               | 85  |

|   | 4.4  | Insula       | ating Materials for Nanoscaled 2D Transistors                                       | 87  |

| 5 | -    |              | ntal Characterization of the Electrical Stability of 2D Transistors                 | 91  |

|   | 5.1  |              | ity of the Threshold Voltage in 2D Transistors                                      |     |

|   |      |              | Hysteresis in $MoS_2$ and Graphene Transistors $\ldots \ldots \ldots \ldots \ldots$ |     |

|   |      |              | BTI in MoS <sub>2</sub> and Graphene Transistors                                    | 101 |

|   |      | 5.1.3        | Tuning the Fermi Level                                                              |     |

|   | 5.2  |              | Pefect Analysis in Nanoscaled 2D Transistors                                        |     |

|   |      | 5.2.1        | RTN in $MoS_2$ Transistors                                                          |     |

|   |      | 5.2.2        | Charge Transfer at Cryogenic Temperatures                                           |     |

|   |      | 5.2.3        | TDDS in $MoS_2$ Transistors                                                         | 121 |

| 6 | Moo  | •            | the Operation and Stability of 2D Transistors                                       | 123 |

|   | 6.1  |              | ling Molybdenum Disulfide Transistors                                               |     |

|   |      | 6.1.1        | Contact Models                                                                      |     |

|   |      | 6.1.2        | Impact of Interface Traps                                                           |     |

|   |      | 6.1.3        | Modeling the Hysteresis                                                             |     |

|   | 6.2  |              | ling Leakage Currents through Gate Insulators                                       |     |

|   |      | 6.2.1        | Adaptations of the Tsu-Esaki Model for hBN                                          |     |

|   |      | 6.2.2        | Coupled DFT and NEGF Model                                                          |     |

|   |      | 6.2.3        | Performance Projection of the Tunnel Current through hBN                            | 140 |

| 7  | Conclusions and Outlook         7.1       Conclusions          |     |  |

|----|----------------------------------------------------------------|-----|--|

| A  | $\textbf{Estimation of the Doping Level in MOCVD grown MoS}_2$ | 151 |  |

| Bi | Bibliography                                                   |     |  |

| Li | List of Publications                                           |     |  |

| Cı | urriculum Vitae                                                | 207 |  |

## Acronyms

| AFM  | atomic force microscopy                 |

|------|-----------------------------------------|

| ALD  | atomic layer deposition                 |

| ALE  | atomic layer etching                    |

| BEOL | back end of line                        |

| BP   | black phosphorus                        |

| BTE  | Boltzmann transport equation            |

| BTI  | bias temperature instability            |

| CAFM | conductive atomic force microscopy      |

| CC   | configuration coordinate                |

| CMOS | complementary metal oxide semiconductor |

| CNT  | carbon nanotube                         |

| CV   | capacitance voltage                     |

| CVD  | chemical vapor deposition               |

| DD   | drift diffusion                         |

| DFT  | density functional theory               |

| DIBL | drain induced barrier lowering          |

| DOS  | density of states                       |

| EOT  | equivalent oxide thickness              |

| FE   | field emission                          |

| FEOL | front end of line                       |

| FET  | field-effect transistor                 |

| GAA  | gate all around                         |

| GFET | graphene field-effect transistor        |

| GGA  | generalized gradient approximation      |

| hBN  | hexagonal boron nitride                 |

| HCD  | hot carrier degradation                 |

| HOPG | highly oriented pyrolytic graphite      |

| LDA  | local density approximation             |

| MBE   | molecular beam epitaxy                            |

|-------|---------------------------------------------------|

| MIS   | metal insulator semiconductor                     |

| MLWF  | maximally localized Wannier function              |

| MOCVD | metal organic chemical vapor deposition           |

| MOS   | metal oxide semiconductor                         |

| MSM   | measure-stress-measure                            |

| NEGF  | non-equilibrium Green's function                  |

| NBTI  | negative bias temperature instability             |

| NMP   | non-radiative multi-phonon                        |

| PA    | photoabsorption                                   |

| PBTI  | positive bias temperature instability             |

| PBE   | Perdew Burke Ernzerhof                            |

| PDF   | probability density function                      |

| PEC   | potential energy curve                            |

| PES   | potential energy surface                          |

| PL    | photoluminescence                                 |

| PS    | photocurrent spectroscopy                         |

| PSD   | power spectral density                            |

| RF    | radio frequency                                   |

| RIE   | reactive ion etching                              |

| RTN   | random telegraph noise                            |

| SB    | Schottky barrier                                  |

| SCE   | short channel effect                              |

| SCL   | surface charge transfer doping                    |

| SEM   | scanning electron microscopy                      |

| SILC  | stress induced leakage currents                   |

| SOI   | silicon on insulator                              |

| SRH   | Shockley-Read-Hall                                |

| SS    | subthreshold swing                                |

| STS   | scanning tunneling spectroscopy                   |

| TAT   | trap-assisted tunneling                           |

| TCAD  | technology computer aided design                  |

| TDDB  | time-dependent dielectric breakdown               |

| TDDS  | time-dependent defect spectroscopy                |

| TE    | thermionic emission                               |

| TEM   | transmission electron microscopy                  |

| TFE   | thermionic field emission                         |

| TLM   | transfer length method                            |

| TMD   | transition metal dichalcogenide                   |

| TSCIS | trap spectroscopy by charge injection and sensing |

| vdW   | van der Waals                                     |

| WKB   | Wentzel-Kramers-Brillouin                         |

| WIND  | wentzer-nramers-brinouni                          |

## List of Figures

| 1.1 | Schematic of an n-type silicon MOSFET including its transfer characteristics.                                                                                                                                                                                                                | 2       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

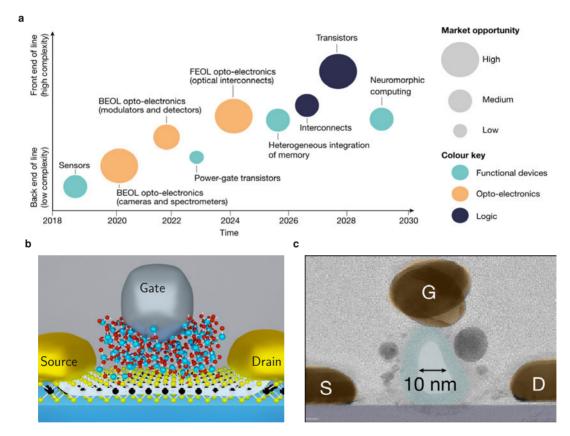

| 1.2 | Market opportunities of 2D material-based devices and schematic structure of a top gated MoS <sub>2</sub> based MOSFET.                                                                                                                                                                      | 7       |

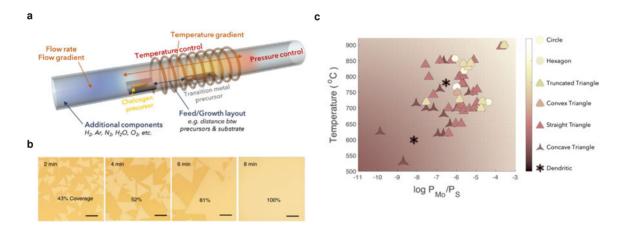

| 2.1 | Chemical vapor deposition (CVD) of TMDs, including a schematic drawing of the CVD furnace, optical microscope images of large area MoS <sub>2</sub> monolayers and the dependence of the growth shape on growth temperature and the ratio of partial precursor pressures.                    | 16      |

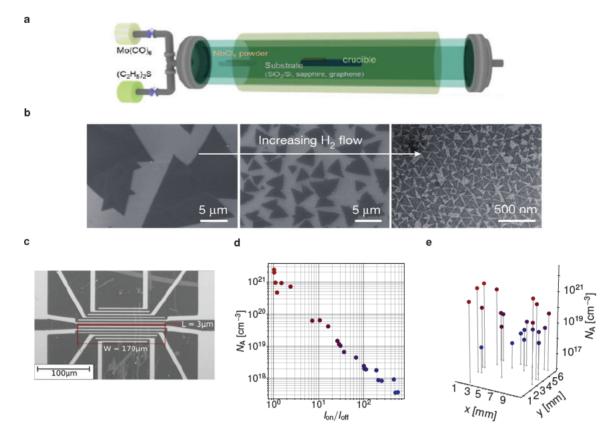

| 2.2 | Metal organic chemical vapor deposition (MOCVD) of TMDs, including a schematic<br>drawing of the MOCVD furnace, SEM and TEM images of grown MoS <sub>2</sub> monolay-<br>ers and fabricated large area MOSFETs based on Nb-doped MoS <sub>2</sub> for evaluating<br>the dopant distribution. | с<br>18 |

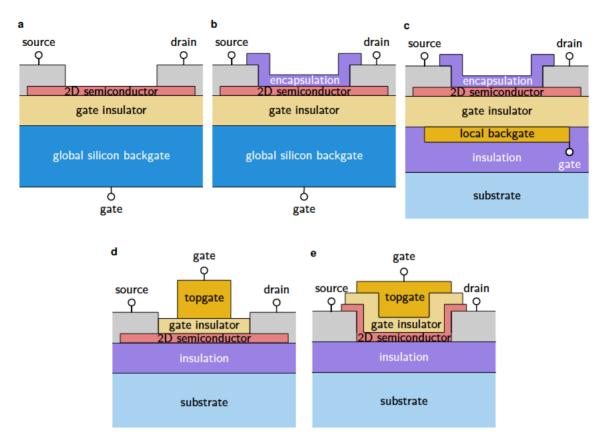

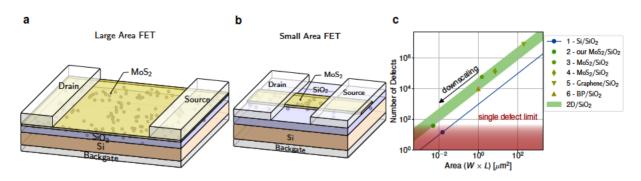

| 2.3 | Cross sections through the five most common 2D semiconductor based FET                                                                                                                                                                                                                       | 10      |

|     | device layouts                                                                                                                                                                                                                                                                               | 24      |

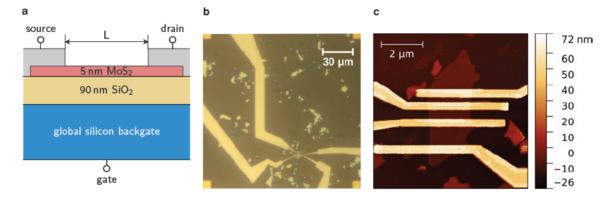

| 2.4 | Fabricated, back gated MoS <sub>2</sub> MOSFETs with a bare channel and SiO <sub>2</sub> as a gate oxide shown in a cross section, optical microscopy and atomic force microscopy                                                                                                            |         |

| 0.5 | images.                                                                                                                                                                                                                                                                                      | 25      |

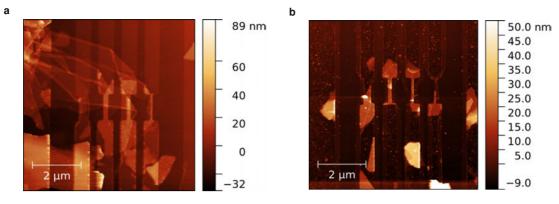

| 2.5 | Comparison of different plasma etch chemistries for etching multilayer $MoS_2$ , showing the AFM images for a layer etched with $SF_6$ /Ar and for a layer etched with $Cl_2/O_2$ .                                                                                                          | 27      |

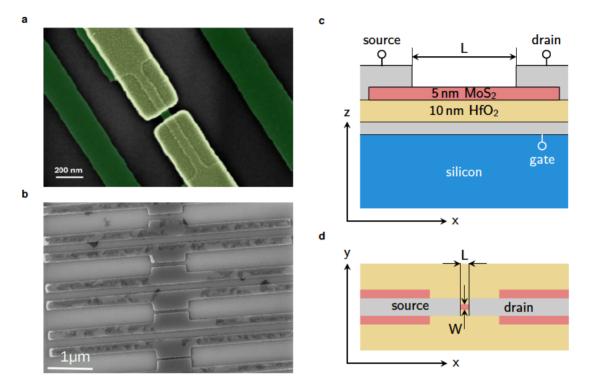

| 2.6 | Fabrication of back gated devices with nanoscaled device dimensions including<br>an SEM of the final device, an SEM image of the dose test pattern and the cross                                                                                                                             |         |

| 0.7 | section and top view shown schematically.                                                                                                                                                                                                                                                    | 29      |

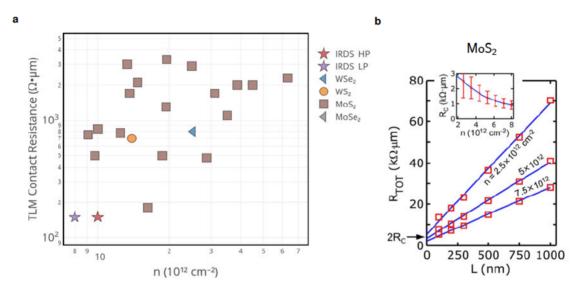

| 2.7 | Transfer length method measurements of the contact resistance to 2D semicon-<br>ductors as reported in literature.                                                                                                                                                                           | 31      |

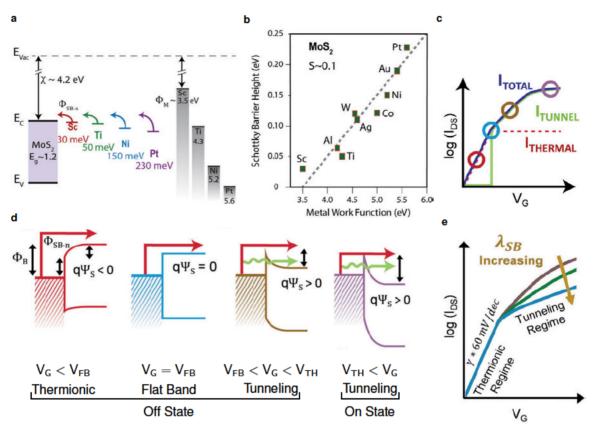

| 2.8 | Schottky barriers form due to strong Fermi level pinning at the metal to semi-<br>conductor contacts. Here the transfer characteristics of Schottky barrier FETs<br>are discussed with respect to the band bending in different regimes                                                      | 34      |

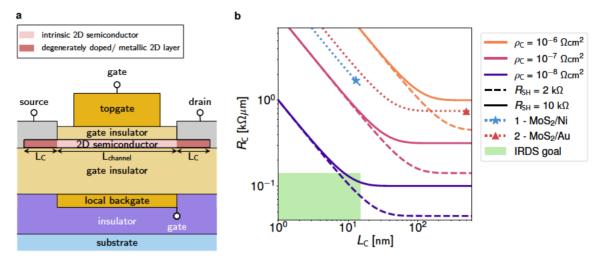

| 2.9 |                                                                                                                                                                                                                                                                                              | 01      |

|     | regions alongside a figure showing the dependence of the contact resistance on the contact length including available literature values.                                                                                                                                                     | 38      |

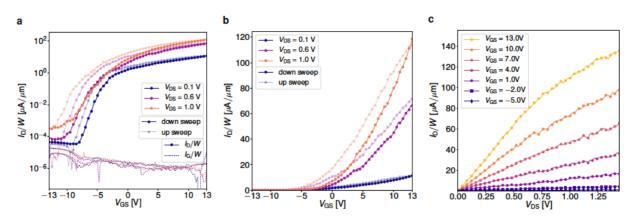

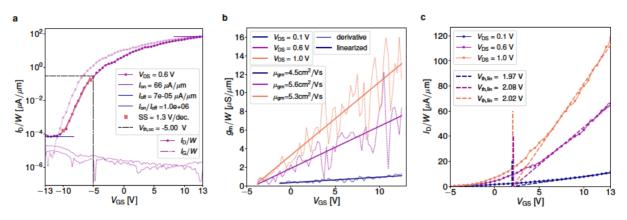

| 3.1 | Standard FET characteristics as measured on an $MoS_2$ FET                                                                                                                                                                                                                                   | 40      |

| 3.2 | Extraction of performance parameters from characteristics measured on an $MoS_2$ FET                                                                                                                                                                                                         | 42      |

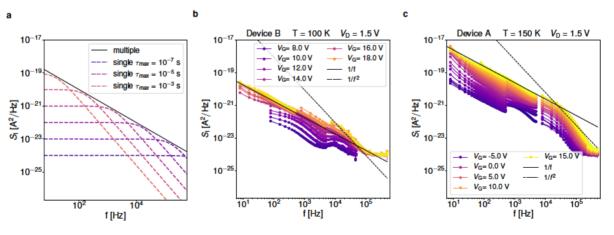

| 3.3 | Low frequency noise on an $MoS_2$ FET and its origin in charge trapping                                                                                                                                                                                                                      | 47      |

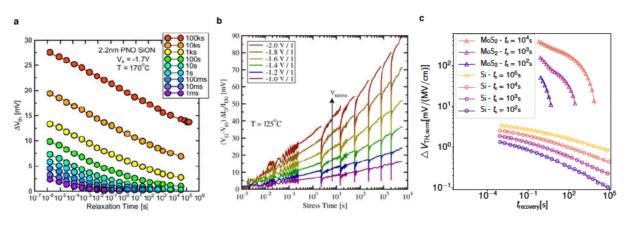

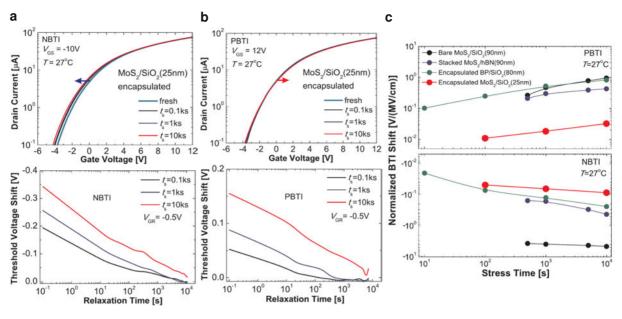

| 3.4<br>3.5                                                                                                             | BTI data for the recovery and stress phases on $Si/SiO_2$ and on $MoS_2/SiO_2$ FETs.<br>Overview of modeling approaches for the simulation of 2D material-based                                                                                               | 50                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

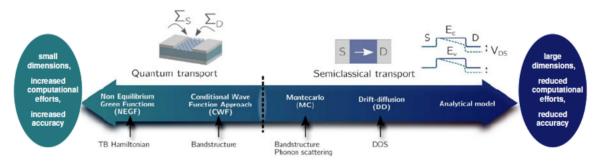

|                                                                                                                        | transistors                                                                                                                                                                                                                                                   | 54                                                                                                                                                                                                                      |

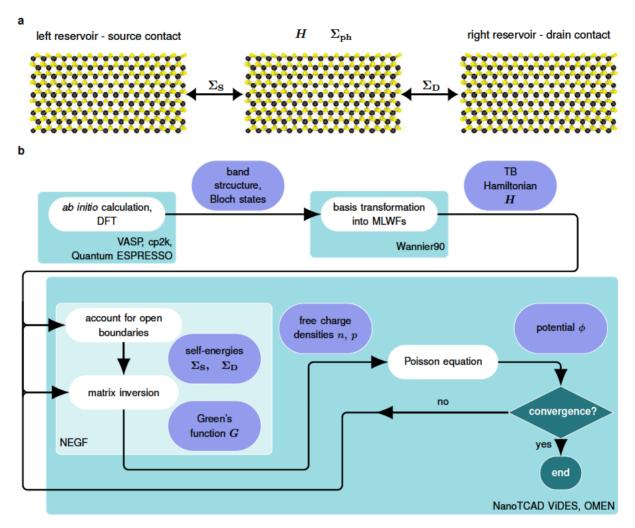

| 3.6                                                                                                                    | Non-equilibrium Green's function modeling of a FET based on a 2D semicon-<br>ducting channel.                                                                                                                                                                 | 56                                                                                                                                                                                                                      |

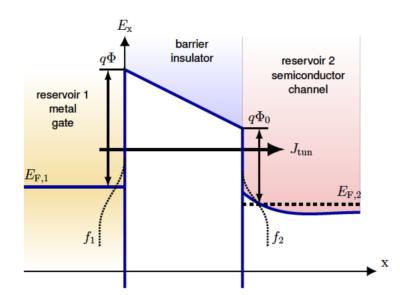

| 3.7                                                                                                                    | Tsu-Esaki model for the tunneling current through an insulating barrier between<br>two reservoirs formed by a metal and a semiconductor.                                                                                                                      | 60                                                                                                                                                                                                                      |

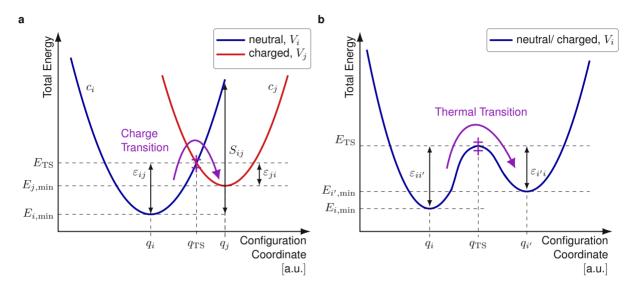

| 3.8                                                                                                                    | Schematic showing the potential energy curves involved for charge transitions and for thermal transitions within NMP theory.                                                                                                                                  | 66                                                                                                                                                                                                                      |

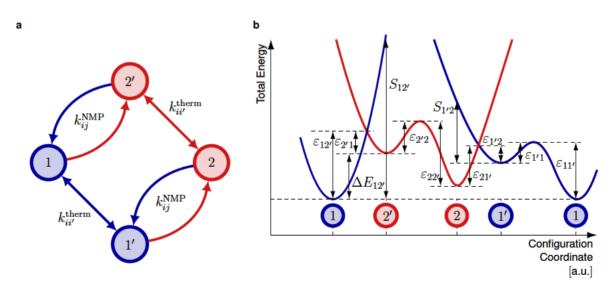

| 3.9                                                                                                                    | States of the 4-state NMP model together with a configuration diagram including all model parameters.                                                                                                                                                         | 69                                                                                                                                                                                                                      |

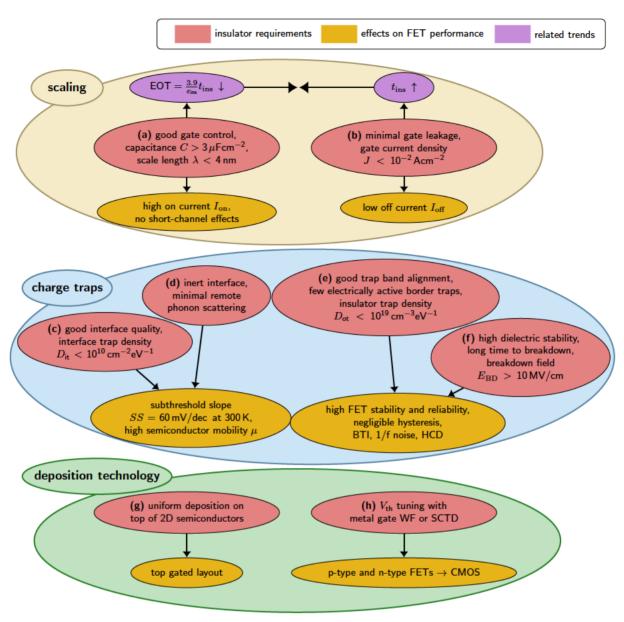

| 4.1                                                                                                                    | Requirements for gate insulators.                                                                                                                                                                                                                             | 74                                                                                                                                                                                                                      |

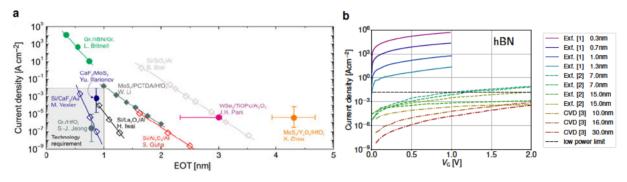

| 4.2                                                                                                                    | Comparison of measured gate leakage current densities as reported in literature.                                                                                                                                                                              | 75                                                                                                                                                                                                                      |

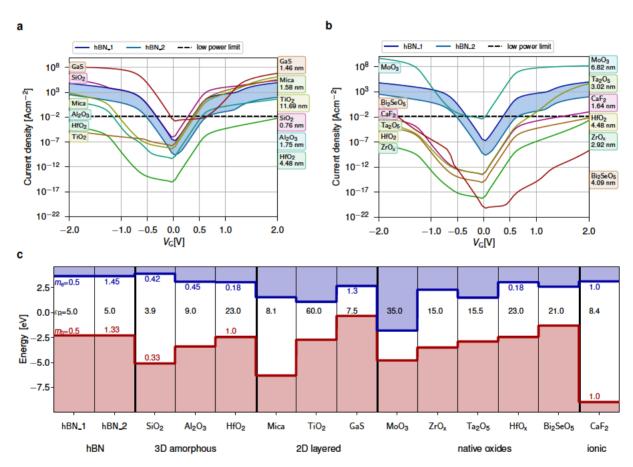

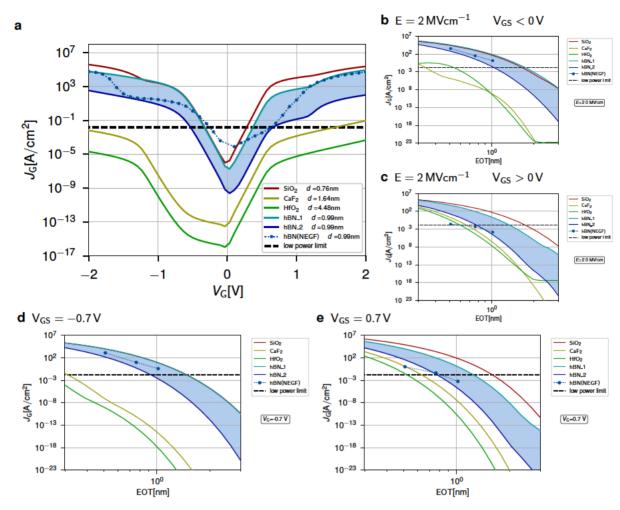

| 4.3                                                                                                                    | Calculated gate leakage current densities through various gate insulators in the ideal, defect-free case.                                                                                                                                                     | 76                                                                                                                                                                                                                      |

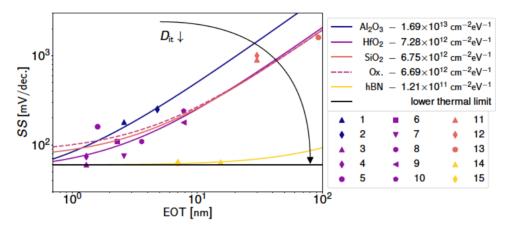

| 4.4                                                                                                                    | Subthreshold swing as a function of EOT as reported in literature.                                                                                                                                                                                            | 79                                                                                                                                                                                                                      |

| 4.5                                                                                                                    | Impact of interface traps and remote phonon scattering on the mobility includ-                                                                                                                                                                                |                                                                                                                                                                                                                         |

|                                                                                                                        | ing a schematic to illustrate the effects of hBN interlayers and a comparison of                                                                                                                                                                              |                                                                                                                                                                                                                         |

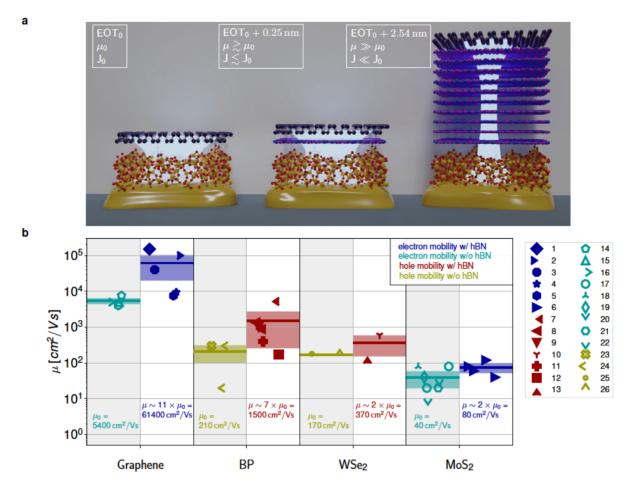

|                                                                                                                        | mobility values with and without an hBN substrate as reported in literature                                                                                                                                                                                   | 81                                                                                                                                                                                                                      |

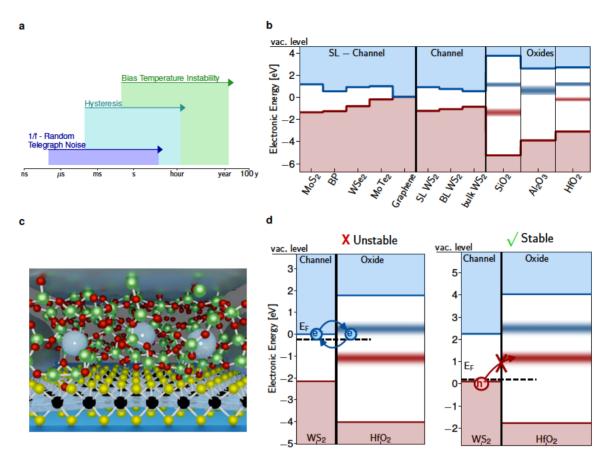

| 4.6                                                                                                                    | Time constants and energetic band alignment of border traps                                                                                                                                                                                                   | 83                                                                                                                                                                                                                      |

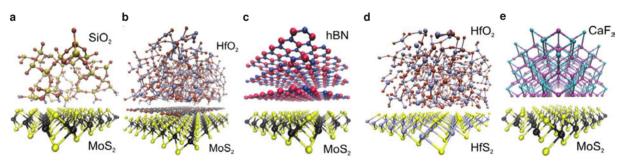

| 4.7                                                                                                                    | Schematic showing the 2D channel/insulator interfaces for various insulators.                                                                                                                                                                                 | 87                                                                                                                                                                                                                      |

|                                                                                                                        |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                         |

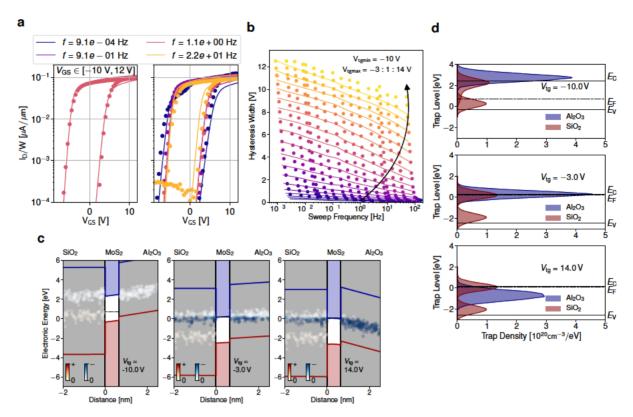

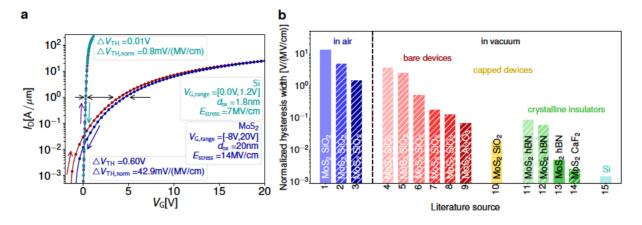

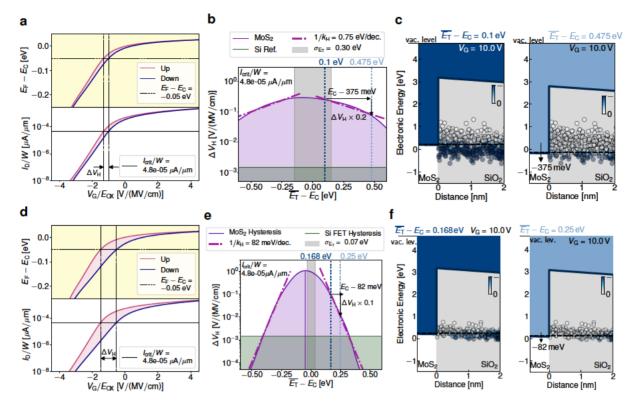

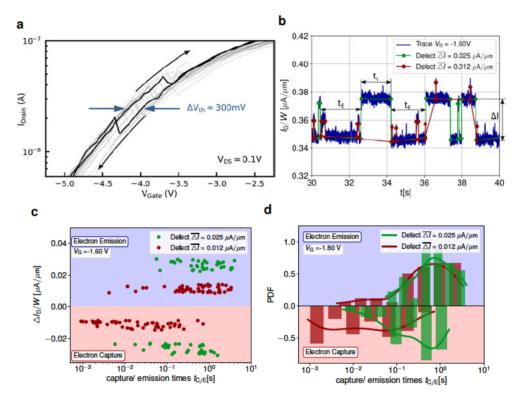

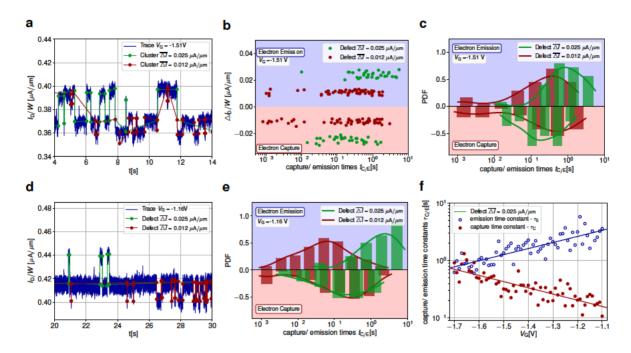

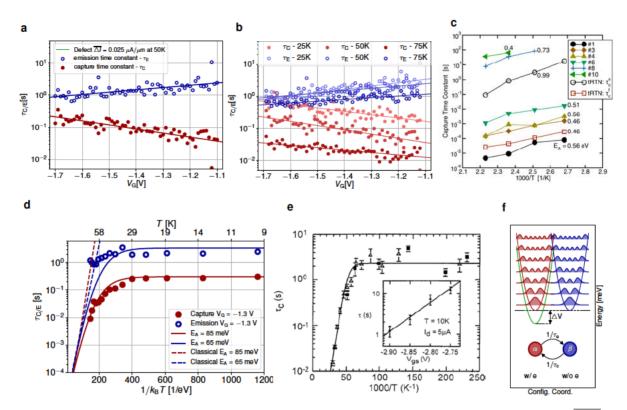

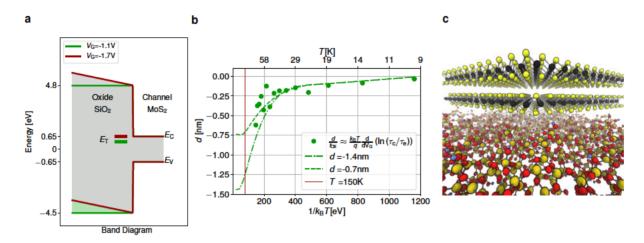

| 5.1                                                                                                                    | Hysteresis measurements in top gated $MoS_2$ FETs with an $Al_2O_3$ gate oxide                                                                                                                                                                                | 94                                                                                                                                                                                                                      |

| 5.1<br>5.2                                                                                                             | Hysteresis measurements in top gated $MoS_2$ FETs with an $Al_2O_3$ gate oxide Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs                                                                                                        | 94<br>95                                                                                                                                                                                                                |

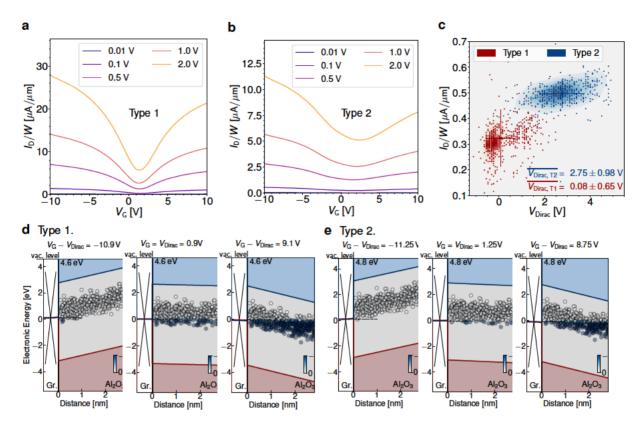

|                                                                                                                        | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide                                                                                                           |                                                                                                                                                                                                                         |

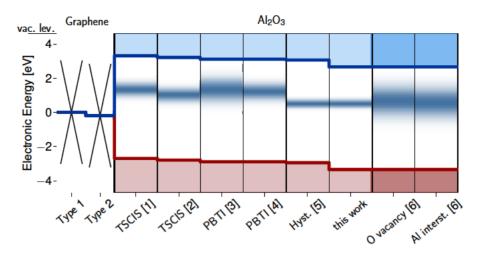

| 5.2                                                                                                                    | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | 95<br>97<br>99                                                                                                                                                                                                          |

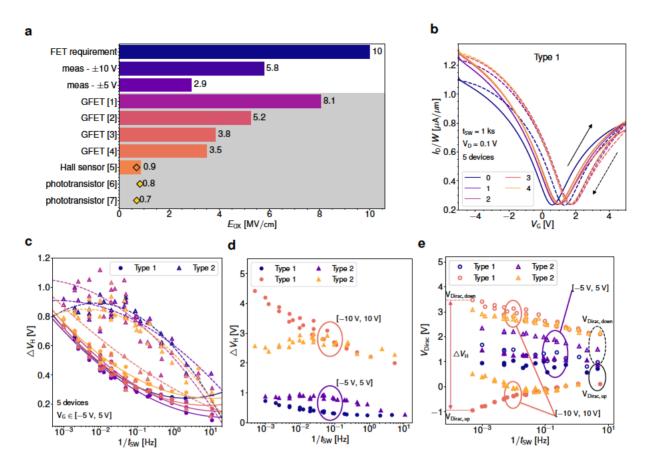

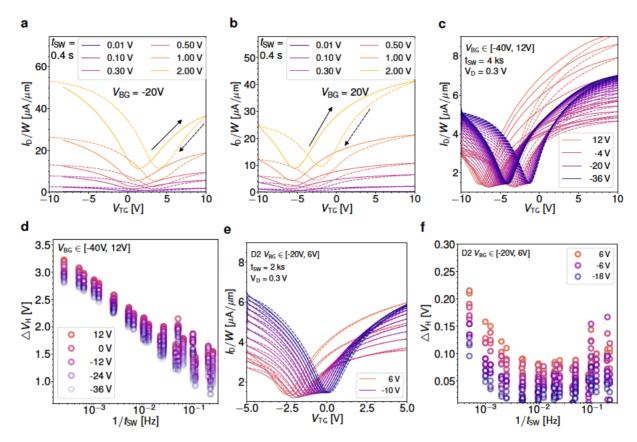

| 5.2<br>5.3<br>5.4<br>5.5                                                                                               | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs.Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide.Defect band alignment in $Al_2O_3$ .Hysteresis in two GFET types at varying sweep times and sweep ranges. | 95<br>97<br>99<br>100                                                                                                                                                                                                   |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                        | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | 95<br>97<br>99<br>100<br>102                                                                                                                                                                                            |

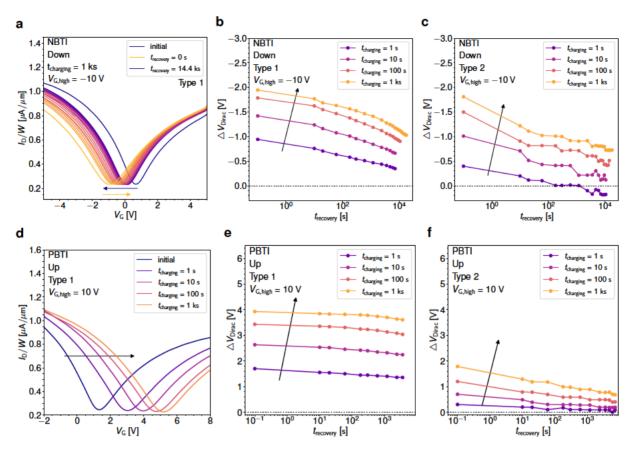

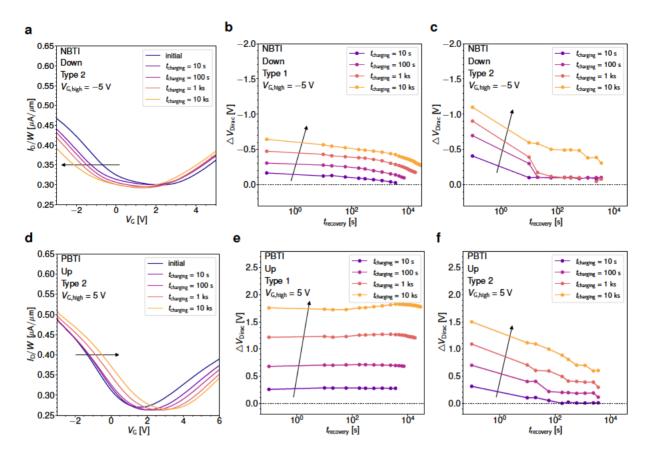

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                 | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | 95<br>97<br>99<br>100<br>102<br>104                                                                                                                                                                                     |

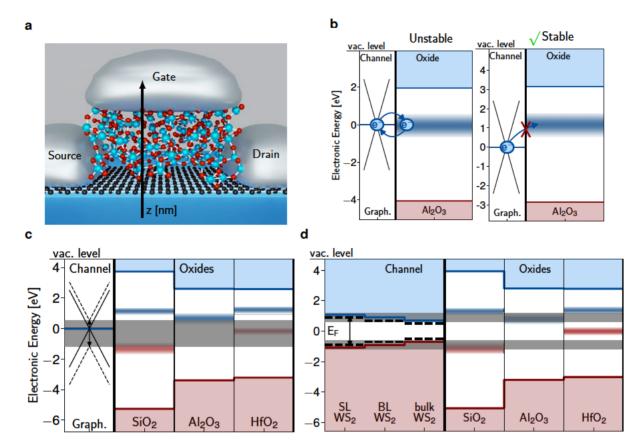

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                                                          | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs<br>Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide<br>Defect band alignment in $Al_2O_3$                                                                  | 95<br>97<br>99<br>100<br>102<br>104<br>105                                                                                                                                                                              |

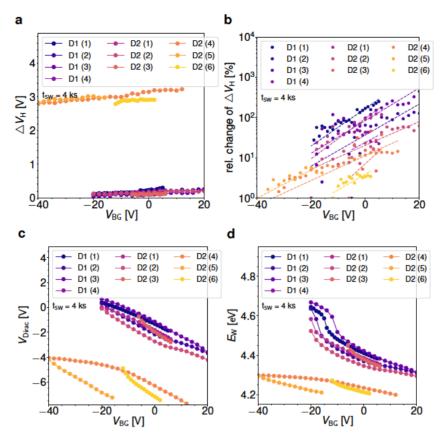

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                                   | Hysteresis widths of MoS <sub>2</sub> FETs in comparison with commercial Si FETs<br>Top-gated GFETs based on two types of graphene with Al <sub>2</sub> O <sub>3</sub> as gate oxide<br>Defect band alignment in Al <sub>2</sub> O <sub>3</sub>               | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107                                                                                                                                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                           | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs<br>Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                     | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107                                                                                                                                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                           | Hysteresis widths of MoS <sub>2</sub> FETs in comparison with commercial Si FETs<br>Top-gated GFETs based on two types of graphene with Al <sub>2</sub> O <sub>3</sub> as gate oxide<br>Defect band alignment in Al <sub>2</sub> O <sub>3</sub>               | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109                                                                                                                                                                |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                   | Hysteresis widths of MoS <sub>2</sub> FETs in comparison with commercial Si FETs<br>Top-gated GFETs based on two types of graphene with Al <sub>2</sub> O <sub>3</sub> as gate oxide Defect band alignment in Al <sub>2</sub> O <sub>3</sub>                  | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109                                                                                                                                                                |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                   | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs<br>Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                     | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109                                                                                                                                                                |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.12                                   | Hysteresis widths of MoS <sub>2</sub> FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with Al <sub>2</sub> O <sub>3</sub> as gate oxide Defect band alignment in Al <sub>2</sub> O <sub>3</sub>                     | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109<br>111<br>112<br>114                                                                                                                                           |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.12<br>5.13<br>5.14                   | Hysteresis widths of MoS <sub>2</sub> FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with Al <sub>2</sub> O <sub>3</sub> as gate oxide Defect band alignment in Al <sub>2</sub> O <sub>3</sub>                     | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109<br>111<br>112<br>114<br>115                                                                                                                                    |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15           | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109<br>111<br>112<br>114<br>115                                                                                                                                    |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15           | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109<br>111<br>112<br>114<br>115<br>117                                                                                                                             |

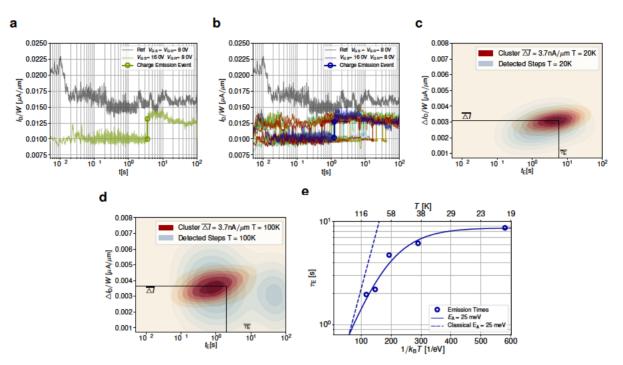

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.112<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16          | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | 95<br>97<br>99<br>100<br>102<br>104<br>105<br>107<br>109<br>111<br>112<br>114<br>115<br>117<br>118                                                                                                                      |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.10<br>5.110<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17 | Hysteresis widths of $MoS_2$ FETs in comparison with commercial Si FETs Top-gated GFETs based on two types of graphene with $Al_2O_3$ as gate oxide Defect band alignment in $Al_2O_3$                                                                        | <ul> <li>95</li> <li>97</li> <li>99</li> <li>100</li> <li>102</li> <li>104</li> <li>105</li> <li>107</li> <li>109</li> <li>111</li> <li>112</li> <li>114</li> <li>115</li> <li>117</li> <li>118</li> <li>120</li> </ul> |

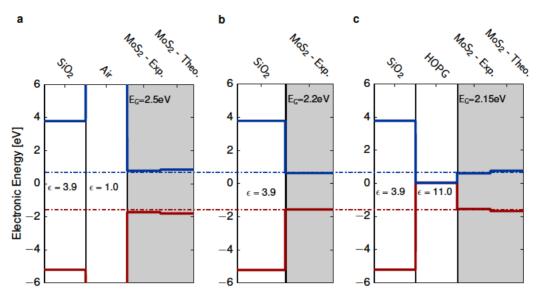

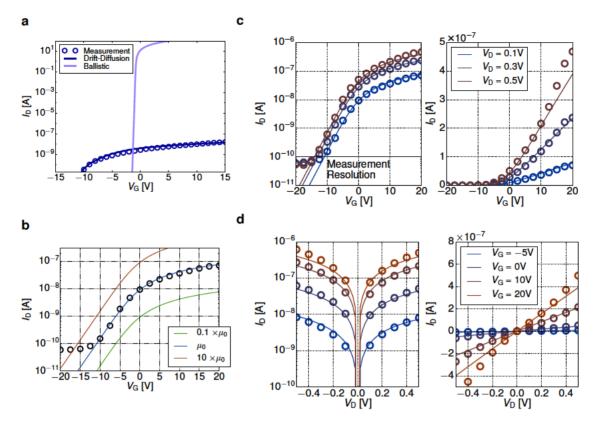

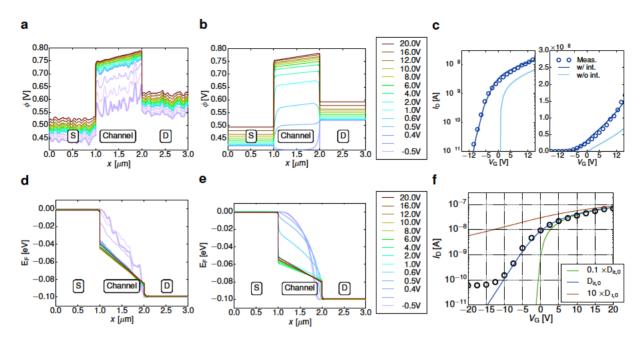

| 6.2  | Drift-diffusion TCAD simulations of MoS <sub>2</sub> FETs                                           | 128 |

|------|-----------------------------------------------------------------------------------------------------|-----|

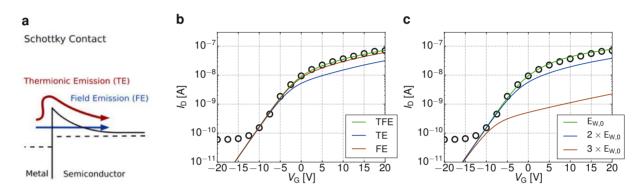

| 6.3  | Schottky contact models as implemented in drift diffusion TCAD simulations                          | 129 |

| 6.4  | Impact of interface traps on $MoS_2$ FETs                                                           | 130 |

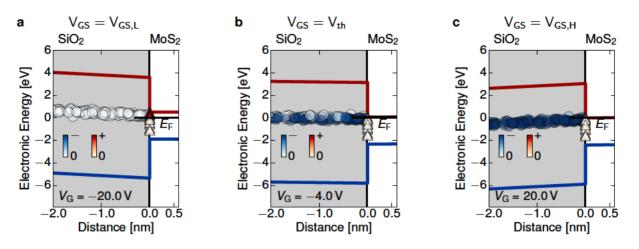

| 6.5  | Band diagram of the MoS <sub>2</sub> /SiO <sub>2</sub> FET showing the alignment of interface traps |     |

|      | and oxide defect bands.                                                                             | 132 |

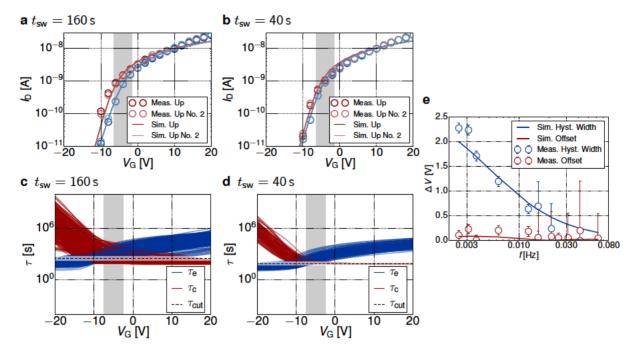

| 6.6  | TCAD simulation of the measured hysteresis using an NMP model                                       | 133 |

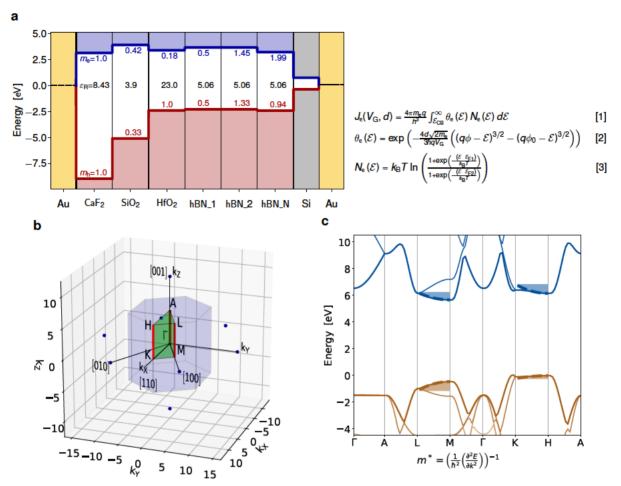

| 6.7  | hBN band structure and adaptations of the Tsu-Esaki model                                           | 136 |

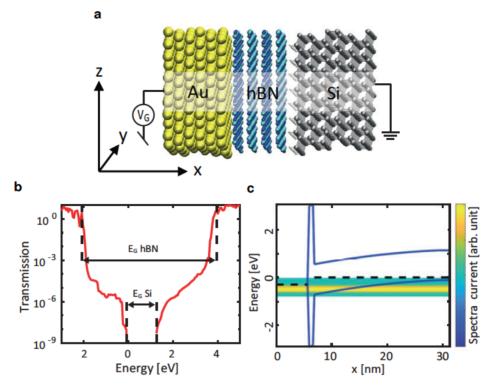

| 6.8  | Ab initio quantum transport calculations.                                                           | 139 |

| 6.9  | Performance projection of the tunneling current through hBN in the defect-free                      |     |

|      | case                                                                                                | 141 |

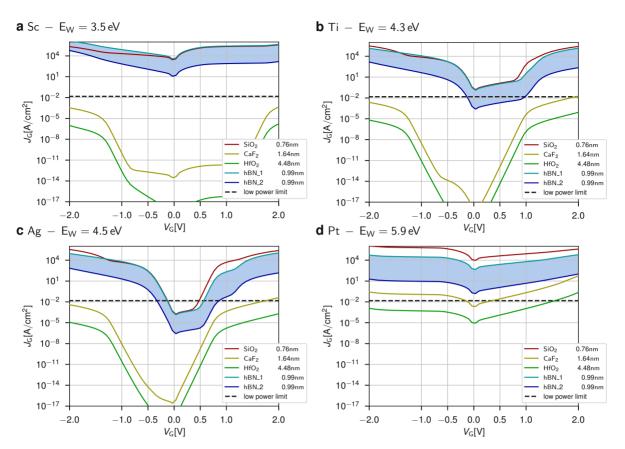

| 6.10 | Impact of the metal work function on the projected current density                                  | 142 |

|      |                                                                                                     |     |

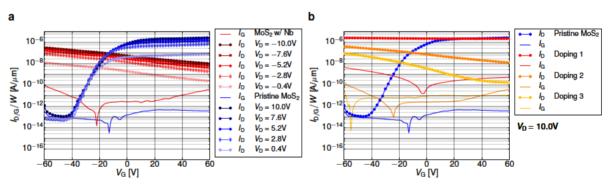

| A.1  | Impact of the Nb doping level on the transfer characteristics of MOCVD grown                        |     |

|      | $MoS_2$ FETs                                                                                        | 151 |

## List of Tables

| 4.1 | Alignment of the known oxide defect bands.                                              | 84  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 4.2 | Comparison of the material parameters of potential gate insulators for 2D CMOS.         | 88  |

| 5.1 | Parameters of the $Al_2O_3$ defect band                                                 | 98  |

| 6.1 | Band gap of monolayer MoS <sub>2</sub> .                                                | 125 |

| 6.2 | Material parameters of MoS <sub>2</sub> monolayers used for drift diffusion based TCAD  |     |

|     | simulations                                                                             | 127 |

| 6.3 | Material parameters of bulk hBN.                                                        | 138 |

| A.1 | Extracted doping levels on different locations of Nb-doped MOCVD grown MoS <sub>2</sub> |     |

|     | film                                                                                    | 153 |

## **1** Introduction

In the ongoing era of the digital transformation, microelectronic chips play an increasingly important role in our society. In fact, microelectronic chips are the backbone of this transformation. Nowadays, economic growth is driven by digital storage of ever increasing amounts of data and converting this data into actionable knowledge [1]. Therefore, making microelectronic chips faster and more versatile is key to economic growth and, more importantly, it is key to exploiting the full potential offered by information technology to solve many problems we face as a society. In addition, as microelectronic chips become cheaper, more people all around the world gain access to the vast amount of data available and to the possibilities and opportunities provided by this technology.

One effective way to work towards faster, cheaper, less energy consuming, and more versatile microelectronic chips is to focus on the transistor, the basic building block of a microelectronic chip. As one microprocessor currently contains up to 40 billion single transistors, powerful scaling laws apply. If transistors themselves are made faster and less energy consuming, while at the same time becoming cheaper, and more easily integrable with memory elements and sensors through monolithic integration, this would be a substantial step towards the goal of more performant, versatile, and accessible microelectronics. Over the last several decades, progress in fabricating faster, more energy-efficient, and cheaper transistors has been made by scaling down the dimensions of silicon-based transistors. In this way, the semiconductor industry has recently started to fabricate microprocessors at the 5 nm node which is a manufacturing generation, associated with a certain transistor size, e.g. 18 nm gate length and 7 nm gate width. At these ultimately small dimensions, the integration of two-dimensional (2D) materials could add considerable value to microprocessors by offering both a promising route towards further downscaling as well as the possibility of diversification of the microelectronic chip [2, 3].

In the introduction of this work, the basic operating principle of FETs is briefly discussed and a historical perspective is provided on the motivation and driving forces behind the continuous downscaling of complementary metal oxide semiconductor (CMOS) logic circuits. This leads to the prospects and ambitions associated with the introduction of 2D materials as building blocks for future transistors. These considerations form the basis for the motivation of this work and the central research question studied. The introduction is finalized by defining the scope of the work and giving a brief outline over the subsequent chapters.

#### 1.1 Field-Effect Transistor

The operating principle of a field-effect transistor is as follows. The voltage applied to a controlling electrode, the gate, creates an electric field which controls the current flow through the semiconducting channel, connecting the source to the drain electrode. Here, the operating principle of the most common variant, the enhancement-mode metal oxide semiconductor field-effect transistor (MOSFET) which is based on a silicon channel is explained. In a MOS-FET, a metal gate determines the electrical potential in the semiconducting channel, which is separated from the gate by the gate oxide. Inside the channel, the current is dominated by carriers of one polarity (only electrons or only holes), thus the MOSFET is a unipolar device. Here, the operation of an n-type MOSFET is described, where an abundance of electrons forms the conducting channel. However, to describe a p-type device only the dopant types would have to be exchanged and the voltage polarities reversed.

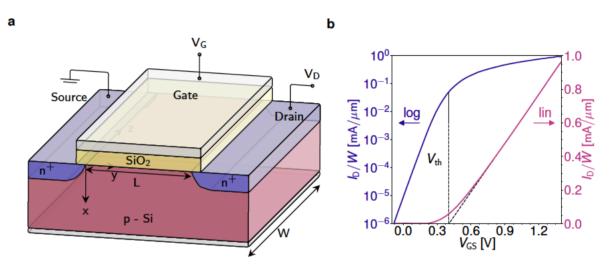

**Figure 1.1.** (a) Schematic drawing of an n-type silicon MOSFET. If a positive bias above the threshold voltage is applied to the gate ( $V_{GS} > V_{th}$ ) an inversion channel forms and the MOSFET turns on. (b) Transfer characteristics of an n-type MOSFET both on a logarithmic (log) and on a linear (lin) scale, indicating the threshold voltage ( $V_{th}$ ). The drain current  $I_D$  is normalized by the transistor width W.

In Figure 1.1(a) an n-type MOSFET is shown in a schematic drawing. It consists of a p-type silicon substrate, where two heavily *n*-doped  $(n^+)$  regions are formed, the source and drain regions. On top of the channel area, between these regions, a thin silicon dioxide (SiO<sub>2</sub>) film is formed via thermal oxidation, the gate oxide. A metal contact on top of the gate oxide serves as the gate electrode. The central element of the MOSFET is formed by the MOS stack, the metal gate, the gate oxide, and the semiconducting silicon channel. In particular, the interface of the channel to the gate oxide is critical for current conduction and for device stability. As long as a negative gate voltage ( $V_{GS}$ ) is applied or  $V_{GS}$  is zero, majority carriers are accumulated in the Si/SiO<sub>2</sub> interface region or the region is depleted. In this accumulation mode, the two back-to-back pn junctions which form the channel block the current flow. Only when a sufficiently large positive voltage  $V_{GS}$  is applied to the channel, the Si/SiO<sub>2</sub> interface is inverted to n-type and thus a conductive inversion channel between the two n<sup>+</sup> regions is formed. If then a voltage is applied to the drain ( $V_{DS}$ ), electrons will flow from source to drain. In a nutshell, a MOSFET operates as a switch, as the gate electrode is insulated from

the channel and turns the channel current on and off via pure capacitive coupling only, which is commonly referred to as the field effect [4]. This behavior of a MOSFET is reflected in its transfer characteristics, where the drain current  $I_D$  (the switched quantity) is given as a function of  $V_{GS}$  (the switching quantity), see Figure 1.1(b). Below the threshold voltage  $V_{th}$ , there is an exponential current increase and once the MOSFET is turned on there is typically a linear dependence of  $I_D$  on  $V_{GS}$ .

A historical perspective on the development of the silicon MOSFET holds insights on the relevant breakthroughs which allow for stable operation of these devices when fabricated in large numbers on an industrial scale. These insights contain some parallels between the important achievements in the early days of silicon MOSFET development and today's development of stable FETs based on 2D materials. Nearly 100 years ago the idea of exploiting the field effect to control the current flow was first described by Lilienfeld in his 1928 patent application [5]. Despite detailed descriptions of amplifier circuits, later attempts to build an amplifying transistor based on Lilienfeld's plans failed and it is unknown whether any of his early prototypes ever provided current amplification [6]. Two decades later, in 1948 at Bell Laboratories a team of engineers consisting of Shockley, Bardeen, and Brattain used a different design to build the first working junction-gate field-effect transistor in the form of a point-contact transistor. This prototype consisted of n-type germanium, connected with two point contacts, which contact the p-type surface inversion layer through a thin oxide [7, 8].

In fact, the engineers at Bell labs had also established a first theory of detrimental surface states, which are called interface traps according to today's nomenclature [9]. They showed that the charge trapping at interface traps was responsible for the weak modulation of the surface potential in thin silicon and germanium semiconductor films, which was orders of magnitude smaller than expected. In their work, they extrapolated the density of interface traps to be as high as  $5 \times 10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> [10], more than 10000 times higher than the standard in today's silicon MOSFETs at  $10^9 \text{ cm}^{-2} \text{eV}^{-1}$ . Soon thereafter in 1952, the reaction kinetics of charge trapping at interface traps were described by Shockley, Read, and Hall in a model formulation which is still used today due to its simplicity [11], see Sections 3.4.1 and 6.1.2. The early MOSFETs showed highly unstable operation for two main reasons. Firstly, they suffered from large interface trap densities which degraded the surface where the current flows in the inversion layer. Secondly, early MOSFETs relied on the introduction of n-type surface inversion in p-type Si and p-type surface inversion in n-type Ge, introduced by weak charging from the air. At that time, the stabilization of MOSFETs was the primary concern for researchers in the field. In 1959, Atalla, Tannenbaum, and Scheibner showed that the surface of silicon pn junctions can be stabilized by thermally grown SiO<sub>2</sub> [12]. This passivation of a silicon pn diode by dry oxidation resulted in a significant reduction in the diode's low frequency noise. More importantly, their discovery of the stabilization of the MOSFET through thermal SiO<sub>2</sub> paved the way towards the first successful operation of an enhancement mode silicon FET [13, 14]. The discovery of the stabilization of MOSFETs using thermal oxidation and the subsequent development of the silicon MOSFET were presumably the most important technological advances which lead to silicon integrated circuits and mass production [6]. It should also be noted that this discovery was made on silicon, whereas most previous discoveries had used germanium due to its higher inherent carrier mobilities. However, since

silicon possesses a stable oxide and the oxide of germanium is water soluble, silicon was used as a basis for the fabrication of integrated circuits, as the operation of silicon MOSFETS was comparatively stable. Hence, the Si/SiO<sub>2</sub> system was central to the success of integrated circuits.

Thus, 30 years after the first mention of the MOSFET concept, the MOSFET in its current form had been designed and built. Already in the same year, Kilby built an integrated circuit to realize a flip-flop out of germanium mesa transistors and gold interconnects [15]. Soon afterwards, the complementary metal oxide semiconductor (CMOS) inverter circuit consisting of an n-type and a p-type MOSFET was invented, which acted as a basic building block for all microprocessor architectures which followed [16]. At that time it also became clear that for the economic success of the novel technology it would be important to significantly reduce the size of electronic circuits. In 1960 Englebart presented the first considerations for scaling laws of electronic circuits [17] and five years later Moore published an article including the projection that the number of transistors on an integrated circuit would double every year [18]. This projection, albeit later adapted, became known as Moore's law and steered the progress in the semiconductor industry over the subsequent five decades. The parallels between the development of the MOSFET described above and today's development of the 2D FET will be detailed when describing the motivation behind this work in Section 1.4.

#### 1.2 CMOS Logic Scaling

Over the last fifty years, the number of transistors per chip has doubled every one-and-ahalf to two years. Moore first hypothesized in 1965 that an exponential growth would drive progress in microelectronics over the next several years [18] and recalibrated the growth rate to a doubling every second year in 1975 [19]. This doubling of the transistor count was realized by reducing the transistor size by a factor of two every two years. A reduction of the transistor size holds many benefits. First, it translates to a reduction of the energy consumed during switching, second, it increases the switching speed, thus the maximum clock frequency of the integrated circuit, and third, it reduces the production costs per single transistor. These benefits, and the pressure to remain economical in a highly competitive market, motivated the semiconductor industry to uphold the mentioned scaling trends. Related efforts for upholding the scaling trends were high and in order to make investments more predictable, in 2000, an industry consortium came together to align their research goals in the form of the International Technology Roadmap for Semiconductors (ITRS) [20]. In the ITRS, roadmap development standards were set and the timelines for future developments were outlined. When further scaling became even more competitive and challenging to uphold, the ITRS was disbanded, with the last report being issued in 2015. In its wake, new efforts were undertaken to address the broader field of progress in electronic devices and systems. These new reports are called the International Roadmap for Devices and Systems (IRDS) and appear annually [21]. IRDS focuses on providing an outline to facilitate the coordination of research and development efforts in the field and sets reference values which will be used throughout this work.

At the core of downscaling lies the idea that the dimensions of transistors can be reduced without degrading key performance characteristics. By reducing the horizontal dimensions of the MOSFET, in particular the channel length, L, the MOSFET becomes easier to switch and requires less chip area. However, if only the horizontal dimensions are reduced, the gate increasingly looses control over the channel, which gives rise to a number of phenomena summarized under short-channel effects (SCEs). Most importantly, the threshold voltage,  $V_{\rm th}$ , becomes dependent on the channel length, being reduced for short L, and the drain bias,  $V_{\text{DS}}$ , starts to have an impact on the drain current as it increasingly modifies the electric field below the gate. These SCEs degrade device performance and consequently the advantages gained by downscaling, unless they are controlled by a suitable device design. In 1974, Dennard et al. suggested that SCEs could be held at bay by maintaining a constant electric field throughout the device while reducing device dimensions [22]. This is realized by scaling down the vertical dimensions along with the horizontal dimensions, by increasing the substrate doping concentration to decrease the depletion width, and by simultaneously decreasing the applied voltages. If all dimensions and applied voltages are scaled down by a factor  $\kappa$ , the circuits are sped up by the same factor and in addition, power dissipation per circuit is reduced by  $\kappa^2$ . However, the requirement of scaling the supply voltage together with the dimensions proved to be too restrictive as it was desirable to maintain the same supply voltage over several technology generations [4]. Instead, the voltage was kept constant, leading to constantvoltage scaling where the electric field increases while the shape of the electric field pattern in the device is preserved to avoid SCEs [23]. Thus, both scaling regimes, constant-field and constant-voltage scaling, can control short channel effects to a certain extent and have been combined in the rules of generalized scaling, where the dimensions scale by a factor  $\kappa$  and the electric field increases by a factor  $\alpha$  [24].

As the circuits were increasingly scaled down, more and more severe physical limitations were observed. There are some quantities central to the operation of MOSFETs which do not scale and set natural limits. First, the thermal voltage  $k_{\rm B}T/q$  is a fundamental property which does not scale and which determines the slope in the subthreshold region [4]. As the slope of the MOSFET's transfer characteristics stays constant instead of increasing beyond the thermal voltage, the on currents decrease as the supply voltage is scaled down. Second, as the silicon bandgap does not scale, the built-in potential and surface potential do not change, which translates to a reduced scaling of the depletion widths and in consequence more severe SCEs. Third, the increase of the electric field has detrimental effects on a number of properties. A higher electric field degrades the mobility, which becomes even more pronounced in thin silicon layers due to surface roughness scattering. Furthermore, higher electric fields in the oxide increase leakage currents and bring the oxide closer to breakdown conditions. In order to maintain small leakage currents while reducing the equivalent oxide thickness (EOT), gate oxides with a higher permittivity ( $\varepsilon_{\rm R}$ ) such as HfO<sub>2</sub> have been introduced. In addition, the oxide thickness has been reduced less than required by scaling laws.

As a whole, all these fundamental limitations have slowed down scaling over recent years and have called for more radical changes to the transistor geometry and the involved materials. A first step to reduce short channel effects was the introduction of the silicon-on-insulator (SOI) substrate. In SOI technology, a conventional MOSFET is built on a thin layer of crystalline

silicon which is separated from the substrate by a several hundred nanometer thick buried SiO<sub>2</sub> film. In this configuration the devices are isolated from the underlying silicon substrate, which results in enhanced gate control [25]. Soon after the first CMOS SOI microprocessor was fabricated in 1997 [26], high gate leakage currents motivated the transition from SiO<sub>2</sub> as a gate oxide with  $\varepsilon_R$  = 3.9 to SiON ( $\varepsilon_R \sim 4.5$ ) [27] and to HfO<sub>2</sub> ( $\varepsilon_R \sim 20$ ) [28, 29] in the production lines. However, even if gate oxides with high permittivity (high-k oxides) allow for further reduction of the EOT at acceptable levels of the leakage currents, further downscaling of dimensions soon exacerbates SCEs. A direct approach to improve SCEs is to change the transistor geometry with the aim of maximizing gate control over the channel. Towards this aim, the gate encloses increasingly more regions of the channel. In a first step a second gate is added below the silicon channel to form a double-gated transistor [30], in the second step the gate encloses the channel from three sides in a finFET geometry [31] and in the third step the gate is wrapped around a silicon nanowire or nanosheet in a gate-all-around (GAA) geometry [32]. Today, the finFET geometry is the state of the art, being used in production since the 22 nm-node in 2012 [33] and dominating the current mass production at the 7 nm node. Over the next five years the GAA geometry might be introduced into fabrication lines at the 3 nm node [34, 35]. Nowadays, the industry has come close to the end of the silicon roadmap, towards ultimately scaled devices, where further scaling requires more significant changes to the device geometry and to the materials used to build MOSFETs. In order to allow for continued shrinking of the gate length a thinner channel is required. In this context, 2D materials are a promising candidate, as they offer atomically thin channels while maintaining sizable electron and hole mobilities [36]. In contrast, in silicon, the channel mobility degrades substantially if the thickness is reduced below 3 nm [37].

#### 1.3 2D Materials Promise Ultimate Thinness

The key benefit of 2D materials is their 2D nature, meaning the fact that they are thermodynamically stable as single atomic layers [38]. Most 2D materials can be fabricated by isolating them from their closely related 3D variants which are characterized by a layered structure. In this structure, the layers are loosely bonded to each other by weak van der Waals forces and show strong covalent bonds only within the single layers. Thus, a single 2D layer does not have any dangling bonds and forms ideally defect-free van der Waals interfaces with other layered materials. Therefore, the charge carrier mobility in 2D materials is comparatively high, as scattering at surface traps is minimized [39, 40]. These high mobilities in addition to the excellent scalability of atomically thin semiconductors as FET channels are the main selling points of 2D materials as channels for FETs in logic applications [3]. A channel with a thickness below 1 nm suppresses short channel effects, thus allowing to scale the channel length below 15 nm [41], required for the beyond 3 nm technology nodes [42].

Besides the advantages of 2D materials used as a channel in a classical MOSFET device design, the van der Waals interface between adjacent layers creates the possibility to combine different 2D materials in van der Waals heterostructures [43]. These heterostructures offer a wide variety of options to create novel device designs [44], among them designs which exploit quantum mechanics to overcome the limitation of the subthreshold slope of FETs