DISSERTATION

# Charge Trapping and Variability in CMOS Technologies at Cryogenic Temperatures

zur Erlangung des akademischen Grades

Doktor der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

JAKOB MICHL

Matrikelnummer 1302759

Betreut von UNIV.PROF. DIPL.-ING. DR.TECHN. TIBOR GRASSER und Assistant Prof. DIPL.-ING. DR.TECHN. MICHAEL WALTL

Wien, im August 2022

## Acknowledgements

First of all, I would like to express my gratitude to **Professor Tibor Grasser**, for the opportunity to do research at the Institute for Microelectronics and for guiding me throughout my PhD study. I am truly grateful that he supported me whenever I needed help and that he motivated and inspired me by always asking the right questions. His passion and enthusiasm for research are contagious and encouraged me during the last years.

I would like to thank **Michael Waltl**, for co-supervising my PhD study and for securing the funding<sup>1</sup> necessary for my employment. He developed the measurement equipment I used for most of my characterization experiments and helped me whenever I encountered issues in the lab. His joy for experimental work made me excited about my experimental work and animated me to explore the boundaries of our setup.

Special thanks go to **Alexander Grill**, who supported me whenever needed, introduced me to all our simulation and measurement tools and had countless valuable discussions with me. He motivated me whenever I struggled during my studies and always strengthened my back. He advised me in innumerable decisions and became a true fried during my research visits at *imec*. Without him, this thesis would not have been possible.

I want to thank my colleagues **Markus Kampl**, **Theresia Knobloch**, **Christian Schleich**, **Bernhard Stampfer**, **Konstantinos Tselios**, and **Dominic Waldhör** for not only providing valuable input, but also for being very good friends.

I also want to thank reasearchers at *imec* with whom I collaborated with, especially **Ben Kaczer**, **Arnout Beckers**, **Dieter Claes**, and **Marko Simičić**. They made the time during my internships fly by.

Last but not least, I would like to thank my family and friends, especially my parents **Gerda** and **Herbert** and my sister **Kristina**. They are there for me when I need them and always have my back. Finally, I want to thank my girlfriend **Lisa**. Your support means the world to me.

<sup>&</sup>lt;sup>1</sup>The financial support by the Austrian Federal Ministry for Digital and Economic Affairs, the National Foundation for Research, Technology and Development, and the Christian Doppler Research Association are gratefully acknowledged.

## CHAPTER 0. ACKNOWLEDGEMENTS

## Abstract

CMOS technology operated at cryogenic temperatures is essential in various fields such as quantum computing (QC), where it serves as a classical control interface for qubits operating in the mK-regime, as host technology enabling a monolithic integration of qubits, or in high-performance computing (HPC) applications. For all these applications, the changing device properties towards cryogenic temperatures must be taken into account in circuit designs. Additionally, potential design optimizations which allow an operation using a very low supply voltage at cryogenic temperatures can be achieved. This is in particular of high interest for QC and HPC to reduce the energy consumption and increase operational frequency. However, the development of robust applications in this field is very challenging for reliability engineers, because their stable operation is very sensitive to drifts of the threshold voltage due to aging and to variability issues. Furthermore, in all applications related to quantum computing, noise originating from charge trapping is very critical, because it can decrease the fidelity of the qubits.

Over the past decades, a deep understanding of the role of defects in the oxide and at the interface between the oxide and substrate has been developed. Such defects can capture and emit a charge which leads to a change in the device electrostatics and are thus responsible for various reliability issues. The charge trapping kinetics can be approximated with the nonradiative multiphonon (NMP) model, which successfully describes the trapping kinetics even at cryogenic temperatures. Since solving the model in its full complexity is computationally expensive, an efficient model has been developed to allow the computation of charge transition rates of thousands of defects and has been implemented in the reliability simulator *Comphy*. This allows to calculate the cumulative response of many defects and enables a comparison of theoretical trap parameters with measurement data. To this end, bias temperature instability and random telegraph noise (RTN) measurements have been conducted between 4 K and room temperature on various technologies. The degradation behavior has been modeled, allowing the extraction of trap parameters and the identification of defect candidates responsible for altering the device electrostatics.

On large-area devices thousands of such traps can be electrically active simultaneously and the superposition of their responses can be measured. In contrast to that, on scaled devices only few traps are active at the same time, which allows to access properties of single defects. Time-dependent defect spectroscopy and RTN studies which are covered in this work show that there is charge trapping even in the limit of cryogenic temperatures. Charge capture and emission rates become temperature independent towards 4 K which is a consequence of nuclear tunneling. This temperature independence of the trapping kinetics in the deep cryogenic regime has been modeled using the NMP model.

While single devices allow to study the physical device degradation mechanisms in detail, a knowledge of the distribution of device performance parameters is essential to qualify a full technology. For this, the characterization of *SmartArrays* with thousands of devices which can be addressed digitally has been performed. This allows the study of the variability of time-zero parameters and its dependence on the temperature. An increasing variability of important device parameters towards 4K can be shown and explained with the occurrence of resonant tunneling which gets more prominent at cryogenic temperatures.

## Kurzfassung

CMOS-Transistoren, die bei Tieftemperaturen betrieben werden, finden Anwendung in vielen Gebieten, wie der Quanteninformatik, wo die Steuerungselektronik für Qubits auf 4 K gekühlt wird, oder als Host-Technologie für eine monolithische Integration mit den Qubits. Auch für Hochleistungsrechner könnte ein Betrieb der CMOS-Logik bei Tieftemperaturen effizient sein. Alle diese Anwendungen basieren auf den temperaturabhängigen Transistoreigenschaften, welche eine Optimierung des Designs für den Betrieb bei Tieftemperaturen erlauben. Mit dem Betrieb der CMOS-Logik bei Tieftemperaturen entstehen neue Herausforderungen für Zuverlässigkeitsingenieur\*innen. So sind Anwendungen im Zusammenhang mit Quantencomputern sehr empfindlich auf Rauschen, welches durch das Einfangen und Emittieren von Ladungen entsteht, und zu Dekohärenz der Qubits führen kann. Darüber hinaus lassen optimierte Designs wenig Spielraum für Variabilität zwischen den einzelnen Transistoren und für Schwellspannungsverschiebungen.

Die Rolle von Defekten im Oxid und an der Oberfläche zwischen Oxid und Substrat wurde in den letzten Jahrzehnten intensiv erforscht. Diese Defekte können Ladungsträger einfangen und emittieren, was zu einer Änderung in der Elektrostatik des Transistors führt und letztendlich die Zuverlässigkeit der Bauteile negativ beeinflusst. Diese Kinetik kann mit dem Nichtstrahlende-Multiphononen-Modell (*engl. nonradiative multiphonon*, NMP) beschrieben werden. Da das vollständige NMP-Modell sehr rechenintensiv ist, wird in dieser Arbeit eine effiziente Näherung präsentiert, welche in den Zuverlässigkeitssimulator *Comphy* implementiert wurde. Das ermöglicht die Berechnung des Einflusses von tausenden Defekten auf die Schwellspannung und einen Vergleich mit experimentellen Daten. Zu diesem Zweck wurde die Spannungs-Temperatur-Instabilität (*engl. bias-temperature-instability*) zwischen 4K und Raumtemperatur mit verschiedenen CMOS-Technologien gemessen. Das Degradationsverhalten wurde anschließend modelliert und mögliche Defektkandidaten wurden identifiziert.

Während in Transistoren mit großen Geometrien tausende von Defekten gleichzeitig aktiv sind, erlauben skalierte Transistoren die Untersuchung von Eigenschaften einzelner Defekte. In dieser Arbeit werden dazu Messungen mit der zeitabhängigen Defektspektroskopie (*engl. time-dependent defect spectroscopy*) und von Telegraphenrauschen (*engl. random telegraph noise*) präsentiert. Diese Messungen zeigen, dass Defekte selbst bei Tieftemperaturen noch Ladungsträger einfangen und emittieren. Die zugehörigen Raten werden temperaturunabhängig, was durch Tunneln zwischen atomistischen Konfigurationen (*engl. nuclear tunneling*) erklärt werden kann.

Einzelne Bauteile bieten die Möglichkeit, physikalische Defektmechanismen zu untersuchen. Um eine Technologie vollständig charakterisieren zu können, ist auch eine Untersuchung der Variabilität der Bauteileigenschaften notwendig. Dazu wurden *SmartArrays* verwendet, die es erlauben, tausende von Transistoren digital anzusteuern. Das ermöglicht die Untersuchung der Verteilung von Transistoreigenschaften und deren Temperaturabhängigkeit. Die Variabilität wichtiger Parameter nimmt bei 4 K zu. Das kann mit Hilfe von resonantem Tunneln erklärt werden, welches bei Tieftemperaturen auftritt.

# Contents

| Acknowledgements ii |                                          |                                                                                                                                                                                         | iii                               |  |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|

| Al                  | Abstract v                               |                                                                                                                                                                                         |                                   |  |

| Kı                  | Kurzfassung vi                           |                                                                                                                                                                                         |                                   |  |

| Co                  | onten                                    | ts                                                                                                                                                                                      | ix                                |  |

| Li                  | st of l                                  | Figures x                                                                                                                                                                               | iii                               |  |

| Li                  | st of A                                  | Abbreviations x                                                                                                                                                                         | vii                               |  |

| 1                   | <b>Intro</b><br>1.1<br>1.2<br>1.3<br>1.4 | oductionField-Effect TransistorCryo-CMOS Applications1.2.1Quantum Computing1.2.2High Performance ComputingReliability and Variability Issues in Cryo-CMOSScope and Outline of this Work | 1<br>2<br>3<br>8<br>9<br>12       |  |

| Ι                   | Mo                                       | deling and Simulation of Defects                                                                                                                                                        | 15                                |  |

| 2                   | <b>Def</b><br>2.1<br>2.2                 | Interface Defects                                                                                                                                                                       | 17<br>17<br>19<br>19<br>22<br>22  |  |

| 3                   | <b>Cha</b><br>3.1<br>3.2                 | Shockley-Read-Hall Model                                                                                                                                                                | <b>25</b><br>26<br>28<br>34<br>40 |  |

|    |      | 3.2.3 Approximation for Undistorted Potential Energy Curves | 45  |

|----|------|-------------------------------------------------------------|-----|

|    | 3.3  | 4-State Nonradiative Multiphonon Model                      | 47  |

| 4  | Reli | ability Modeling                                            | 49  |

|    | 4.1  | Electrostatics of MOS Structures                            | 49  |

|    | 4.2  | Defect Distribution in the Oxide                            | 50  |

|    |      |                                                             | 00  |

| II | D    | efect Characterization at Cryogenic Temperatures            | 55  |

| 5  | Mea  | asurement Setup and Technologies                            | 57  |

|    | 5.1  | Measurement Setup                                           | 57  |

|    | 5.2  | Investigated MOS Transistor Technologies                    | 58  |

|    | 5.3  | Characterization of <i>SmartArray</i> Structures            | 59  |

| 6  | Tim  | e-Zero Characterization                                     | 63  |

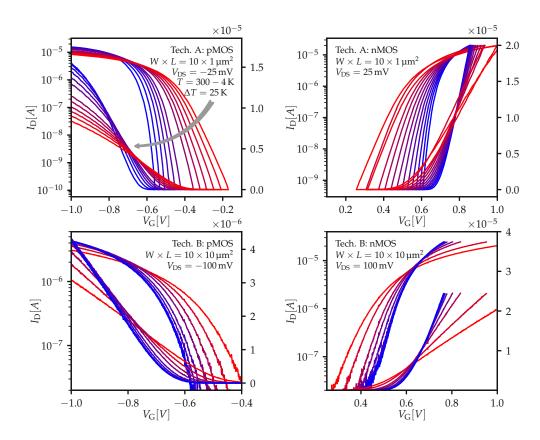

| U  | 6.1  | Transfer Characteristics                                    | 63  |

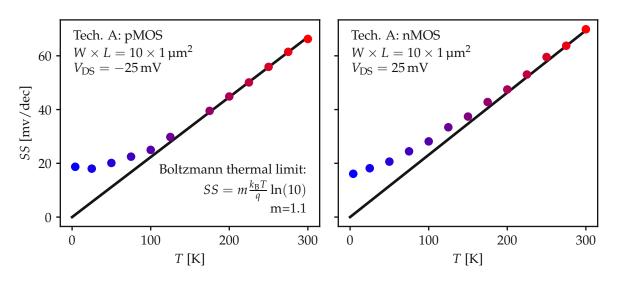

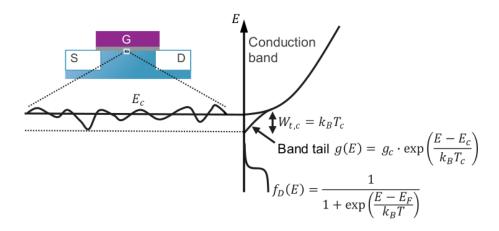

|    | 0.1  | 6.1.1 Subthreshold Swing                                    | 64  |

|    |      | 6.1.2   Transconductance                                    | 67  |

|    |      | 6.1.3 Threshold Voltage                                     | 67  |

|    |      | 6.1.4 ON-State Current                                      | 69  |

|    | 6.2  | Capacitance-Voltage Measurements                            | 69  |

|    | 6.3  | Resonant Tunneling at Cryogenic Temperatures                | 70  |

|    | 6.4  | Variability Characterization                                | 72  |

|    |      | 6.4.1 Variability Study on <i>SmartArray A</i>              | 72  |

|    |      | 6.4.2 Variability Study on <i>SmartArray B</i>              | 75  |

| 7  | Cha  | rge Noise Characterization                                  | 87  |

|    | 7.1  | Experimental Characterization                               | 87  |

|    | 7.2  | 1/f Noise                                                   | 88  |

|    | 7.3  | Random Telegraph Noise                                      | 90  |

|    |      | 7.3.1 Canny Edge Detector                                   | 91  |

|    |      | 7.3.2 Otsu's Method                                         | 92  |

|    | 7.4  | RTN in SiON Devices                                         | 94  |

|    |      | 7.4.1 Temperature and Gate Voltage Variation                | 95  |

|    | 7.5  | RTN in MoS <sub>2</sub> MOSFETs                             | 100 |

|    | 7.6  | RTN in the Resonant Tunneling Region                        | 102 |

| 8  | Bias | s Temperature Instability                                   | 107 |

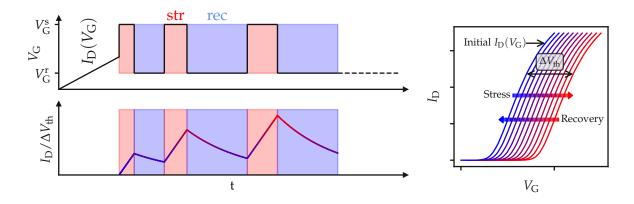

|    | 8.1  | Extended Measure-Stress-Measure Scheme                      | 108 |

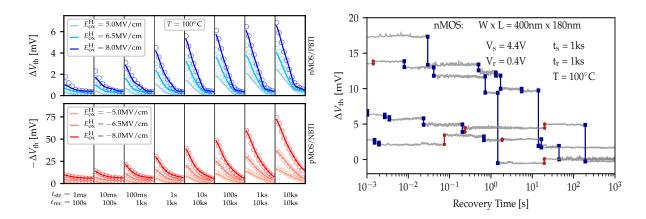

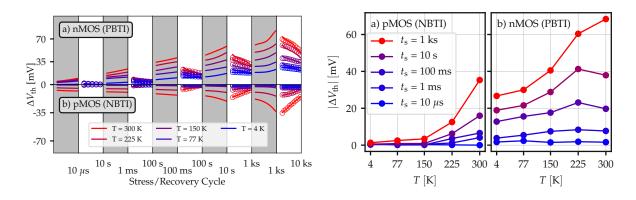

|    | 8.2  | Temperature Dependence of BTI Measurements                  | 109 |

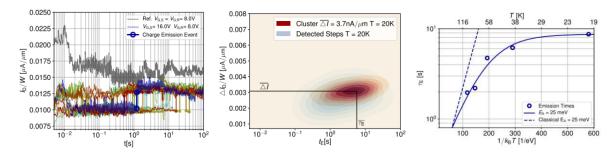

|    | 8.3  | TDDS Measurements at Cryogenic Temperatures                 | 116 |

|    |      |                                                             |     |

| 9                       | Con        | clusion and Outlook | 119 |  |

|-------------------------|------------|---------------------|-----|--|

|                         | 9.1        | Conclusion          | 119 |  |

|                         | 9.2        | Outlook             | 121 |  |

|                         |            |                     |     |  |

| Α                       | App        | endix               | 123 |  |

|                         | A.1        | WKB Approximation   | 123 |  |

|                         | A.2        | Saddlepoint Method  | 124 |  |

| References 127          |            |                     |     |  |

| Ne                      | Kererences |                     |     |  |

| List of Publications 15 |            |                     | 151 |  |

# **List of Figures**

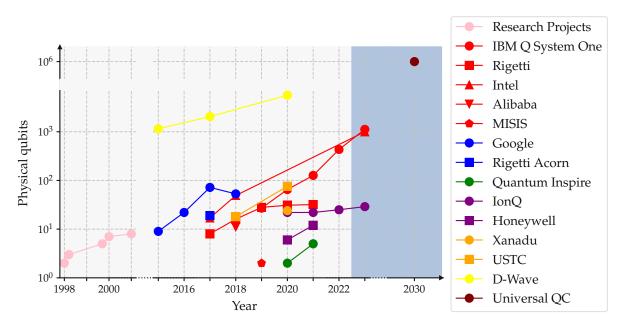

| 1.1  | Historical overview of physical qubits                                               | 3  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | Mathematical representation of a qubit as Bloch sphere and realization of            |    |

|      | a quantum computer by IBM                                                            | 5  |

| 1.3  | SEM images of Si electron spin qubit and superconducting qubit                       | 6  |

| 1.4  | Development towards a monolithic co-integration of qubits and cryo-                  |    |

|      | CMOS                                                                                 | 7  |

| 1.5  | Temperature dependent transition curve for high performance computing                | 9  |

| 1.6  | Schematic representation of degradation mechanisms in the $\{V_G, V_D\}$ -space      | 10 |

| 2.1  | $P_{b0}$ and $P_{b1}$ center at the (100) oriented Si/SiO <sub>2</sub> surface       | 18 |

| 2.2  | Density of states and band edges at $Si/SiO_2$ interface                             | 19 |

| 2.3  | Atomistic configurations of oxygen vacancy, hydrogen bridge and hydroxyl-            |    |

|      | E' center                                                                            | 20 |

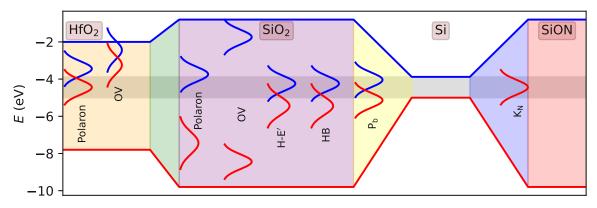

| 2.4  | Trap level distribution of various defect candidates in $SiO_2$ , $HfO_2$ and $SiON$ | 21 |

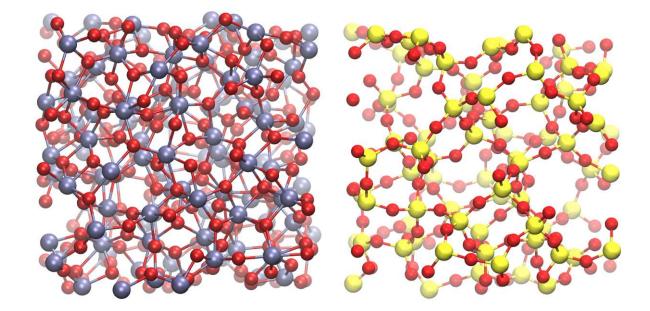

| 2.5  | Atomistic structures of a-HfO <sub>2</sub> and a-SiO <sub>2</sub>                    | 23 |

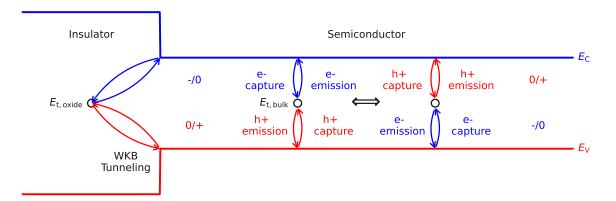

| 3.1  | Overview of charge capture and emission processes                                    | 27 |

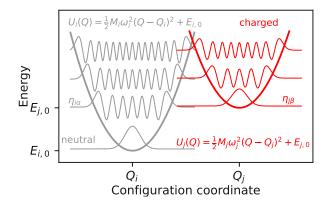

| 3.2  | Configuration coordinate diagram of potential energy surfaces with their             |    |

|      | respective vibrational eigenfunctions                                                | 31 |

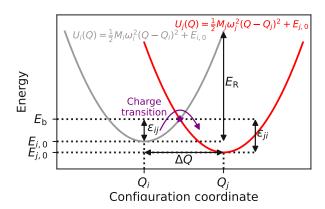

| 3.3  | Configuration coordinate diagram for a charge transition in the classical            |    |

|      | limit                                                                                | 33 |

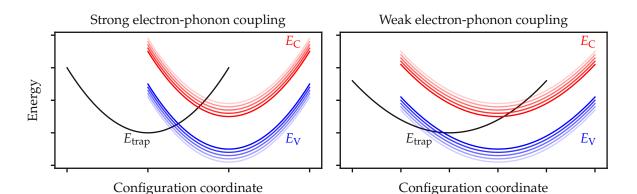

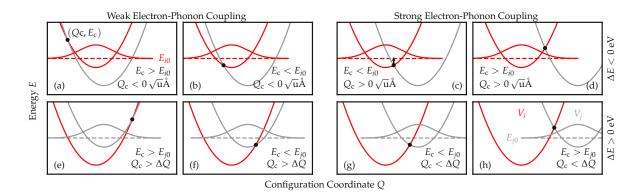

| 3.4  | Strong and weak electron-phonon coupling                                             | 34 |

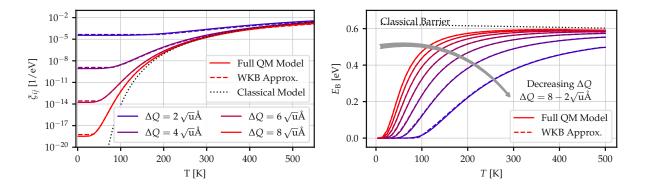

| 3.5  | WKB approximation for vibrational wave functions                                     | 36 |

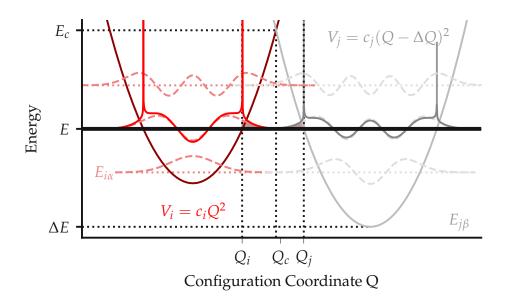

| 3.6  | Relative positions of the potential energy surfaces in the 2-state model .           | 37 |

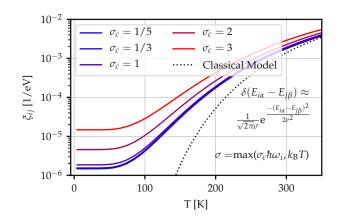

| 3.7  | Lifetime broadening of Dirac-delta distribution                                      | 41 |

| 3.8  | Lineshape function and effective barrier lowering between 4 K and 500 K              | 41 |

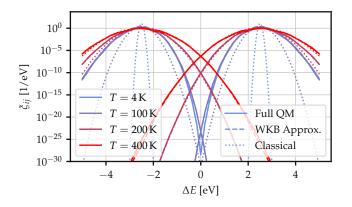

| 3.9  | Energy offset dependence of lineshape function                                       | 42 |

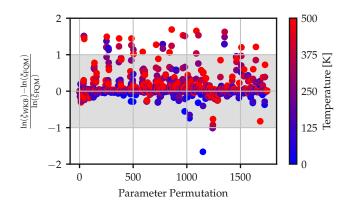

| 3.10 | Benchmark of WKB based against full quantum mechanical lineshape                     |    |

|      | function                                                                             | 43 |

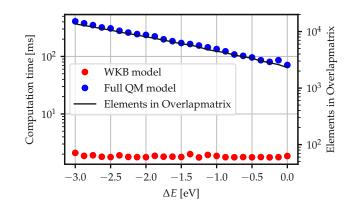

| 3.11 | Comparison of computation time of full quantum mechanical and WKB                    |    |

|      | based lineshape function                                                             | 44 |

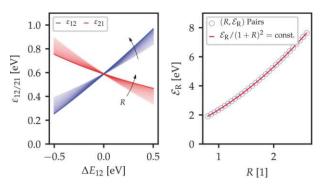

|      | Charge transition barriers for various $(R, E_R)$ -pairs                             | 45 |

| 3.13 | Lineshape function for undistorted potential energy curves                           | 47 |

|            | Anomalous random telegraph noise                                                                                                                   | 47<br>48 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1<br>4.2 | Impact of oxide defect on electrostatics                                                                                                           | 52       |

| 4.3        | position                                                                                                                                           | 52<br>53 |

| 5.1        | Cryogenic probe station and custom built measurement box                                                                                           | 58       |

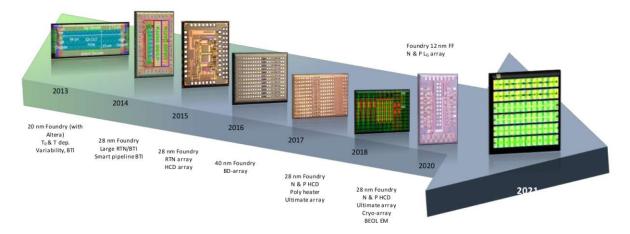

| 5.2        | Development of <i>SmartArrays</i>                                                                                                                  | 60       |

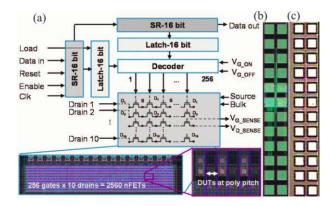

| 5.3        | <i>SmartArray</i> circuit topology for 2017 tape-out                                                                                               | 60       |

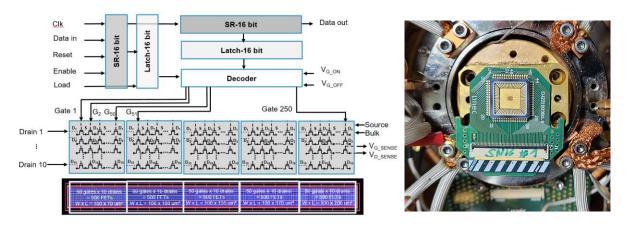

| 5.4        | <i>SmartArray</i> circuit topology for 2018 tape-out                                                                                               | 61       |

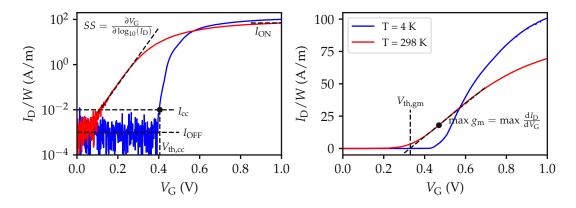

| 6.1        | Schematic $I_D(V_G)$ for room and cryogenic temperatures                                                                                           | 64       |

| 6.2        | Temperature dependence of the transfer characteristics of <i>Tech. A</i> and                                                                       |          |

|            | <i>Tech.</i> B                                                                                                                                     | 65       |

| 6.3        | Temperature dependence of subthreshold swing of <i>Tech. A</i>                                                                                     | 65       |

| 6.4        | Band tail states caused by crystalline disorders                                                                                                   | 66       |

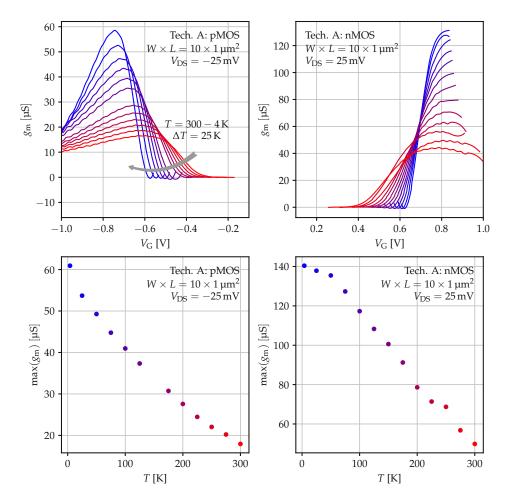

| 6.5        | Temperature dependence of transconductance of <i>Tech. A</i>                                                                                       | 68       |

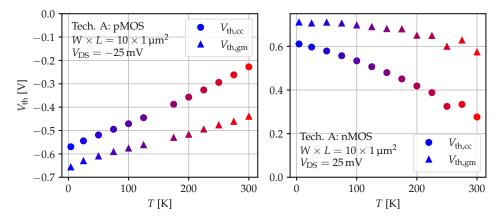

| 6.6        | Temperature dependence of threshold voltage of <i>Tech. A</i>                                                                                      | 69       |

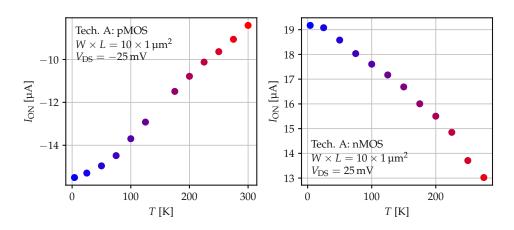

| 6.7        | Temperature dependence of ON-state current of <i>Tech. A</i>                                                                                       | 70       |

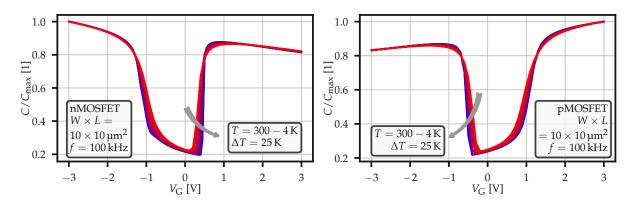

| 6.8        | CV-characterization of <i>Tech. B</i>                                                                                                              | 71       |

| 6.9        | Resonant tunneling at cryogenic temperatures                                                                                                       | 71       |

|            | Negative transconductance in resonant tunneling regime                                                                                             | 72       |

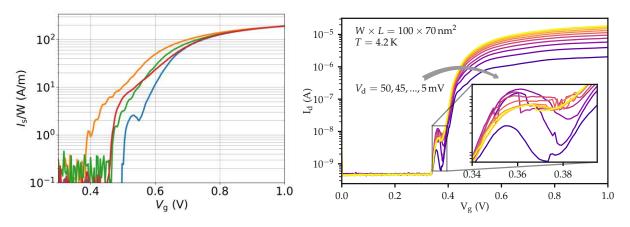

|            | Transfer characteristics measured on <i>SmartArray A</i>                                                                                           | 73       |

|            | Quantile plots of $V_{\text{th}}$ , SS, $I_{\text{ON}}$ and $\max(g_{\text{m}})$ measured on SmartArray A.                                         | 74       |

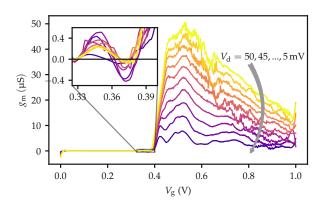

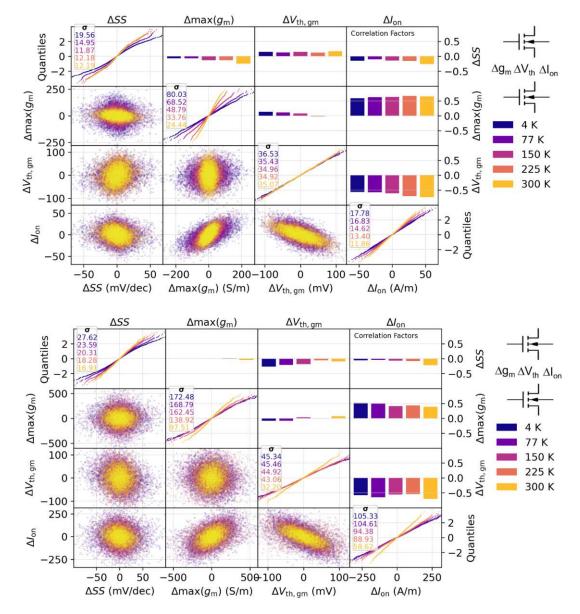

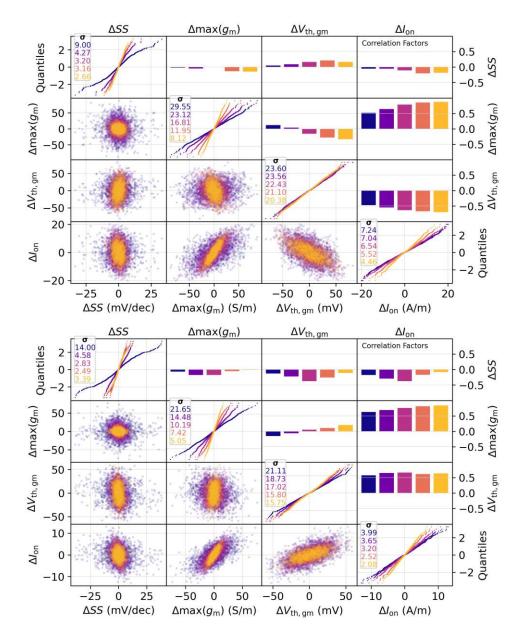

|            | Deivce parameter correlation plots of <i>SmartArray A</i>                                                                                          | 76       |

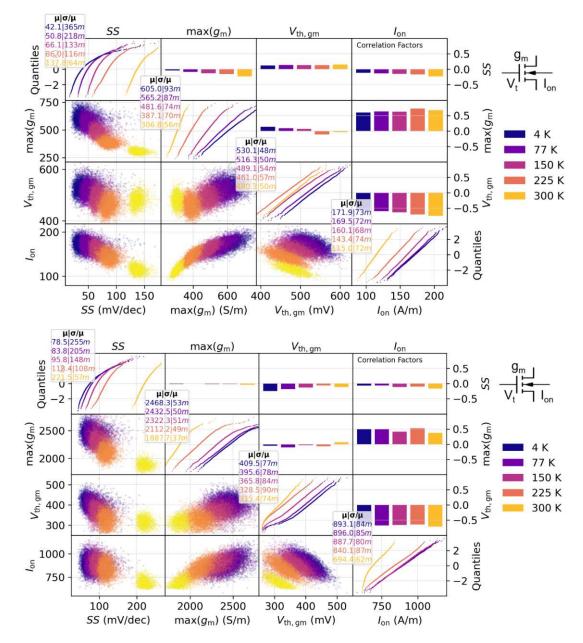

|            | Device parameter mismatch plots of <i>SmartArray A</i>                                                                                             | 77       |

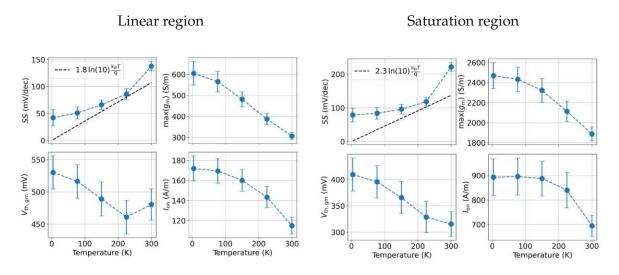

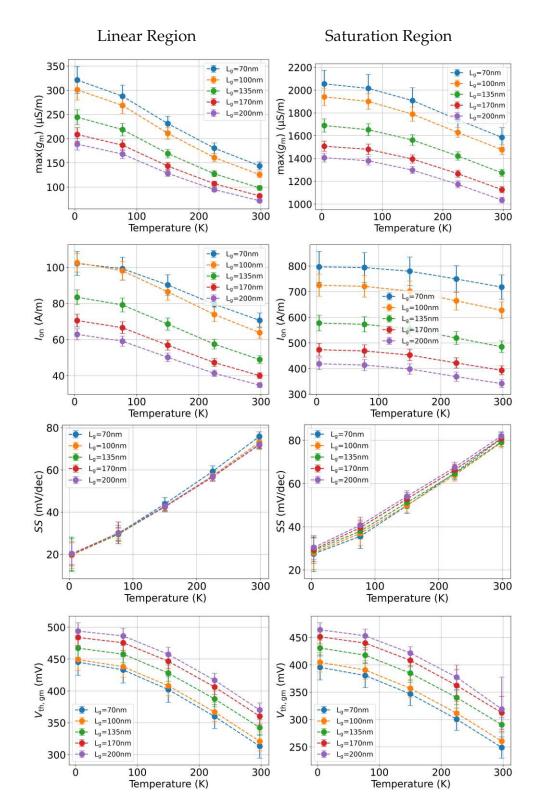

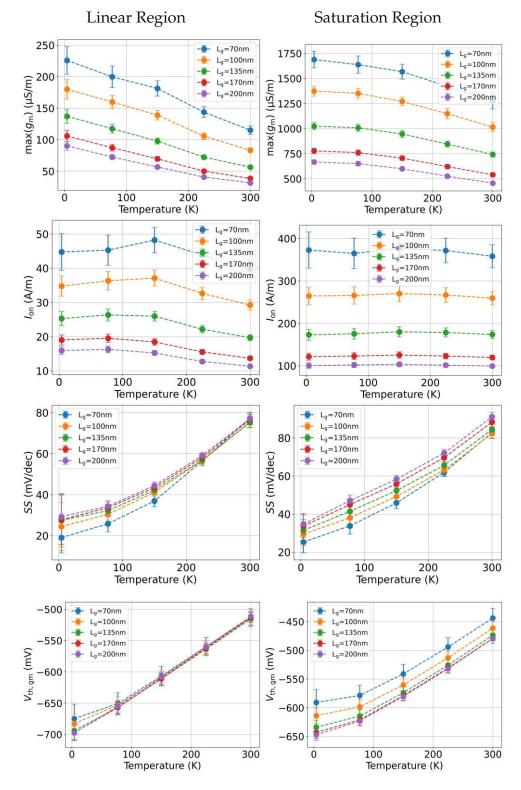

|            | Mean values of $SS$ , max $(g_m)$ , $V_{\text{th}}$ and $I_{\text{ON}}$ of $SmartArray A$                                                          | 78       |

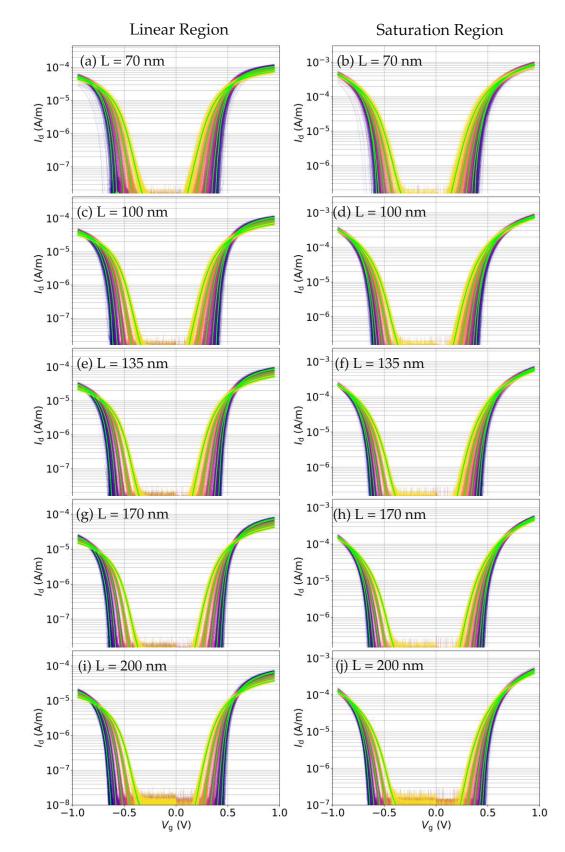

| 6.16       | Set of measured transition curves of <i>SmartArray B</i> in the linear and                                                                         |          |

| (17        | saturation regime                                                                                                                                  | 79       |

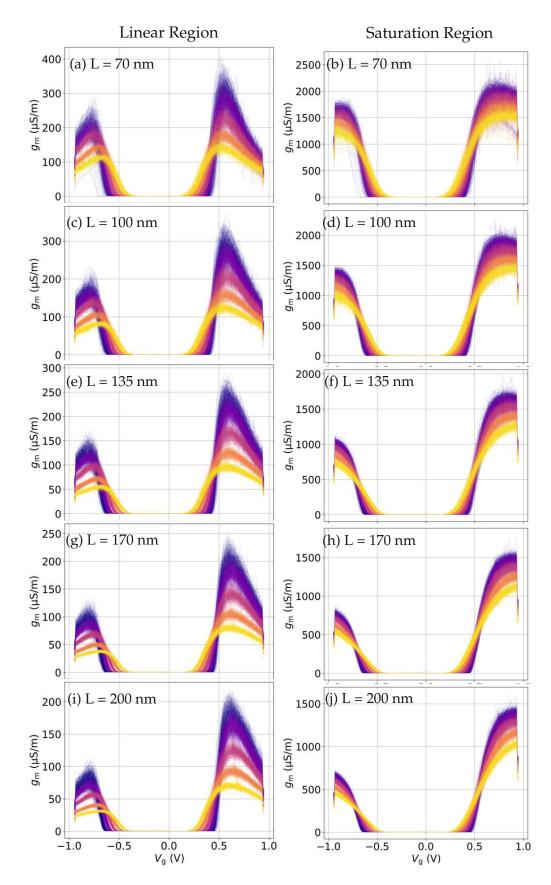

| 6.17       | Variability of transconductance curves recorded on <i>SmartArray B</i> in the                                                                      | 00       |

| ( 10       | linear and saturation regime                                                                                                                       | 80       |

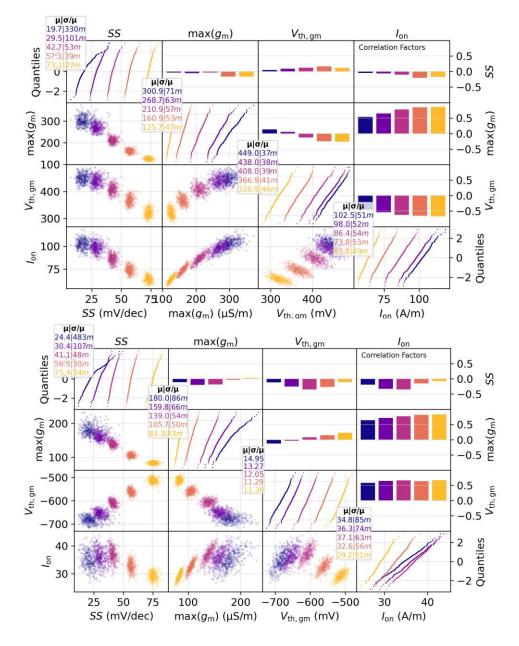

| 6.18       | Correlation plot of nMOS and pMOS transistors of <i>SmartArray B</i> with $M_{VV} I_{V} = 100 \text{ mm} \times 70 \text{ mm}$                     | 01       |

| ( 10       | $W \times L = 100 \text{ nm} \times 70 \text{ nm}$                                                                                                 | 81       |

| 0.19       | Mismatch plot of nMOS and pMOS transistors of <i>SmartArray B</i> with $M \times L = 100$ nm $\times 70$ nm                                        | on       |

| 6.20       | $W \times L = 100 \text{ nm} \times 70 \text{ nm}$                                                                                                 | 82       |

| 0.20       | Temperature and lengths dependence of <i>SS</i> , $V_{\text{th}}$ , $\max(g_{\text{m}})$ and $I_{\text{ON}}$ extracted of nMOS <i>SmartArray B</i> | 84       |

| 6 21       | Temperature and lengths dependence of <i>SS</i> , $V_{\text{th}}$ , $\max(g_{\text{m}})$ and $I_{\text{ON}}$ ex-                                   | 04       |

| 0.41       | tracted on pMOS <i>SmartArray B</i>                                                                                                                | 85       |

|            |                                                                                                                                                    | 00       |

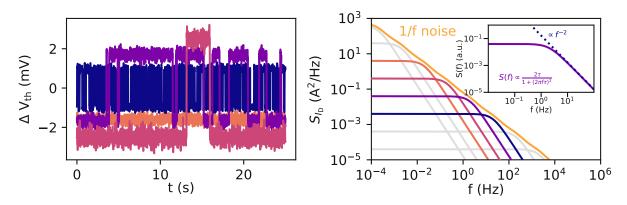

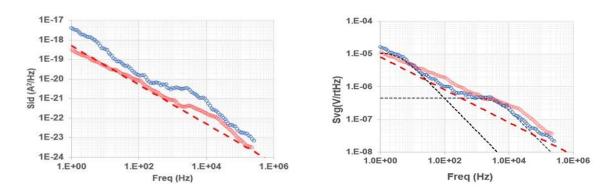

| 7.1        | RTN signals and corresponding power spectral densities                                                                                             | 88       |

| 7.2  | 1/f noise at room and cryogenic temperature                                                      |

|------|--------------------------------------------------------------------------------------------------|

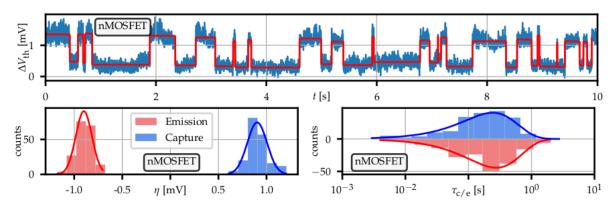

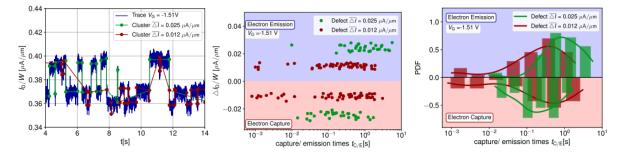

| 7.3  | Defect extraction from RTN signals                                                               |

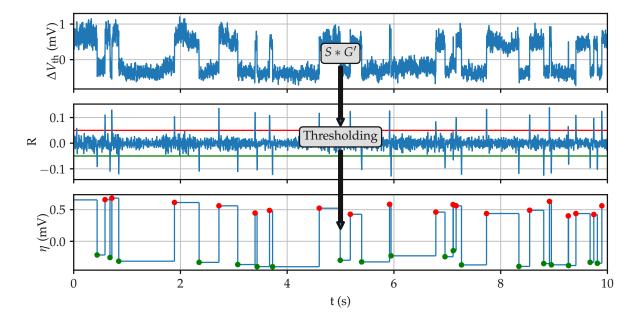

| 7.4  | Step detection using the Canny algorithm                                                         |

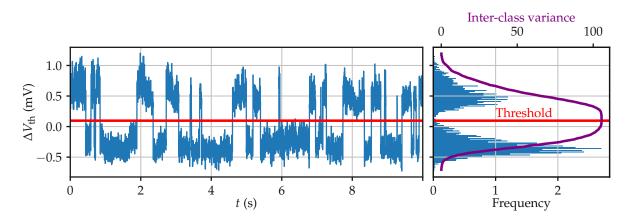

| 7.5  | Threshold value detected with Otsu's method                                                      |

| 7.6  | Limits of step extraction for high gate voltages and high temperatures . 95                      |

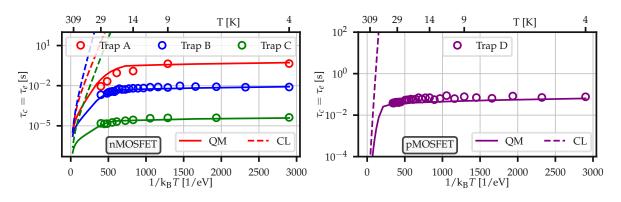

| 7.7  | Capture and emission time extraction at cryogenic temperatures 97                                |

| 7.8  | Dependence of extracted step heights on gate voltage and temperature . 98                        |

| 7.9  | Extracted time constants of defect A and D                                                       |

| 7.10 | Temperature independent charge transition region at cryogenic tempera-                           |

|      | tures                                                                                            |

| 7.11 | Band diagrams showing active RTN defects at cryogenic temperatures . 100                         |

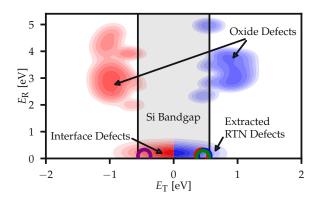

| 7.12 | $(E_{\rm T}, E_{\rm R})$ -heatmap showing the active regions for oxide and interface defects 100 |

| 7.13 | RTN characterization on $MoS_2$ devices                                                          |

| 7.14 | Temperature dependence of time constants measured on $MoS_2$ devices . 102                       |

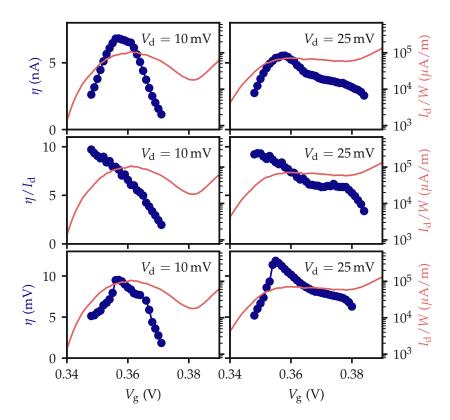

|      | Resonant tunneling at selected drain voltages                                                    |

|      | Parameter extraction of RTN signal in the resonant tunneling regime 103                          |

| 7.17 | Extracted time constants of measured RTN signals in resonant tunneling                           |

|      | regime                                                                                           |

| 7.18 | RTN trap lying outside of the resonant tunneling region 105                                      |

| 7.19 | Extracted step heights of measured RTN signals in resonant tunneling                             |

|      | regime                                                                                           |

| 8.1  | Extended measure-stress-measure scheme                                                           |

| 8.2  | Continuous $\Delta V_{\text{th}}$ on large area devices vs. discrete steps on scaled devices 110 |

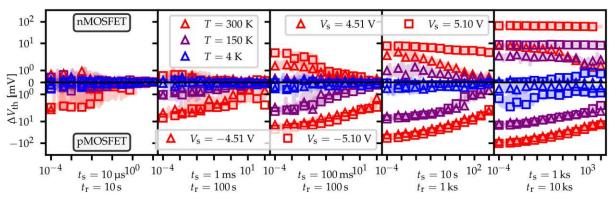

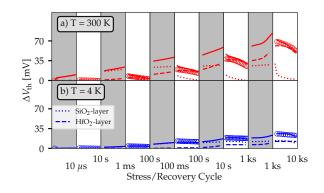

| 8.3  | NBTI and PBTI on <i>Tech. B</i> between cryogenic and room temperature 110                       |

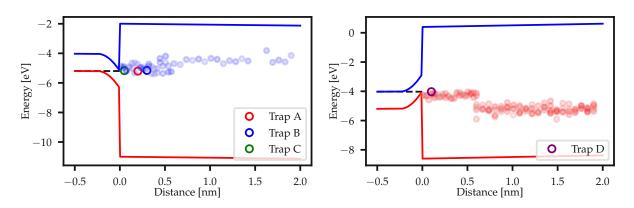

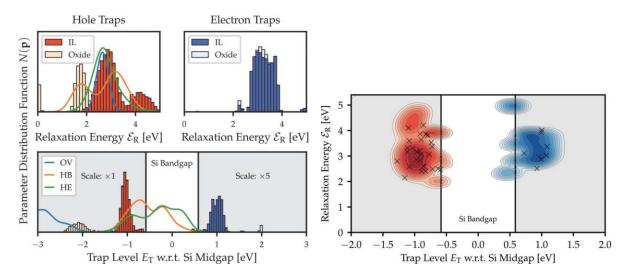

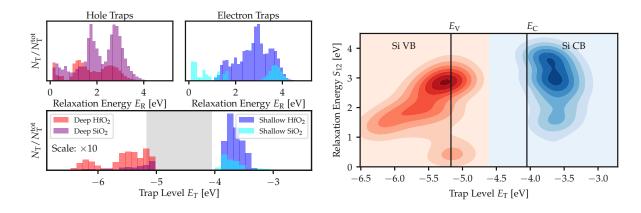

| 8.4  | $(E_{\rm T}, E_{\rm R})$ -heatmap extracted from BTI measurements on <i>Tech. B</i> 111          |

| 8.5  | NBTI and PBTI on <i>Tech. A</i> between room and cryogenic temperatures 112                      |

| 8.6  | $(E_{\rm T}, E_{\rm R})$ -heatmap extracted from BTI measurements on <i>Tech. A</i> 113          |

| 8.7  | Contribution of each trap band to total threshold voltage shift at room                          |

|      | and cryogenic temperatures                                                                       |

| 8.8  | Defect contributions to NBTI and PBTI at room and cryogenic temperatures114                      |

| 8.9  | Asymmetry of charge trapping kinetics caused by trap level distribution 115                      |

| 8.10 | Temperature dependent time constants of defect ensemble 116                                      |

| 8.11 | TDDS measurements on MoS <sub>2</sub> devices                                                    |

## **List of Abbreviations**

aRTN anomalous random telegraph noise ASIC application-specific integrated circuit BTI bias temperature instability CCR closed cycle refrigirator MOS **CMOS** complementary MOS **CSA** charge sheet approximation CV capacitance-voltage DFT density functional theory DIBL drain induced barrier lowering DUT device under test eMSM extended MSM EOT equivalent oxide thickness **ESiD** effective single defect decomposition FET field-effect transistor **HCD** hot carrier degradation **HKMG** high- $\kappa$  metal gate HPC high-performance computing imec Interuniversity Microelectronics Centre IRDS International Roadmap for Devices and Systems **ITRS** International Technology Roadmap of Semiconductors IV current-voltage JJ Josephson junction MOS metal-oxide-semiconductor MOSFET MOS field-effect-transistor **MSM** measure stress measure NMP non-radiative multi-phonon **NNLS** non-negative least square OTF on-the-fly PDK process design kit PEC potential energy curve PES potential energy surface **PNO** plasma-nitrided oxides

| PSD   | power spectral density             |

|-------|------------------------------------|

| QC    | quantum computing                  |

| QD    | quantum dot                        |

| qubit | quantum bit                        |

| RT    | room temperature                   |

| RTN   | random telegraph noise             |

| RTS   | random telegraph signal            |

| SEM   | scanning electron microscope       |

| SEPC  | strong electron-phonon coupling    |

| SET   | single electron transistor         |

| SPM   | saddlepoint method                 |

| SRH   | Shockley–Read–Hall                 |

| TCAD  | technology computer-aided design   |

| TDDS  | time-dependent defect spectroscopy |

| VLSI  | very large-scale integration       |

| WEPC  | weak electron-phonon coupling      |

| WKB   | Wentzel-Kramers-Brillouin          |

|       |                                    |

# Chapter 1

## Introduction

The *Digital Revolution* goes hand in hand with the rise of the modern semiconductor industry and was enabled by the invention of metal-oxide-semiconductor field-effective transistors (MOSFETs) as the backbones of digital circuits. This would not have been possible without understanding and exploiting effects of quantum mechanics. The development of quantum physics and the resulting scientific and technological break-throughs in the 20<sup>th</sup> century are therefore often called the *First Quantum Revolution*. Currently, we are in the middle of the *Second Quantum Revolution*, where devices actively operate with quantum states with the ultimate goal of developing a universal quantum computer [1]. In the following chapter, the role of MOSFETs operated at cryogenic temperatures (cryo-CMOS) and the related challenges will be discussed, setting a special focus on quantum computing (QC) and high-performance computing (HPC). In this context, especially the role of reliability issues in cryo-CMOS devices will be highlighted. The chapter will close by presenting the scope and outline of this thesis.

### **1.1 Field-Effect Transistor**

The *Digital Revolution* would not have been possible without the field-effect transistor (FET), whose invention started in the early days of the 20<sup>th</sup> century. Around 1925, the Austrian physicist Julius Edgar Lilienfeld started to develop the idea and theoretical description on how to use the field effect to modulate the conductivity in a semiconductor triode structure resulting in a patent application in 1928 [2]. Only seven years later, in 1935, the German Physicist Oskar Heil patented the first insulated-gate FET [3]. However, it is unknown whether Lilienfeld or Heil were able to realize a working transistor as proof of concept [4]. From 1948 on developments accelerated when the first junction-gate FET patent was filed by Bell Labs, as suggested by Brattain, Bardeen and Shockley [5]. However, it was not until the 1960s when first MOSFETs where fabricated by Kahng [6] and Atalla [7]. While the first structures suffered from large variations due to a high density of interface defects [8], manufacturing processes improved rapidly and commercially fabricated transistors became available in 1964 by Fairchild and by RCA [4]. Already 1963 the researchers Sah and Wanlass from Fairchild suggested a new type of MOSFET logic combining both nMOS and pMOS, called complementary MOS (CMOS) [9], and filed a patent which was granted in 1967 [10]. This new logic allowed logic circuits operating at significantly lower power consumption and became the de facto standard fabrication process for very-large-scale integration (VLSI) chips in the 1970s. Since then, many improvements of the processing steps, material systems involved and circuit technology enabled to reduce the feature size from the  $\mu$ m-range to a few nm nowadays. For this, the lithography process was improved to enable the fabrication of gate lengths smaller than wavelength of the used UV light. Furthermore, along many other optimizations, new gate and insulator materials such as high- $\kappa$  dielectrics were introduced and the geometry was improved to non-planar transistors (e.g. FinFETs, GAA FETs).

All these improvements in the fabrication process for manufacturing smaller feature sizes, are summarized in what is today well-known as *Moore's law*. In 1965 Gordon Moore, who is a co-founder of Fairchild and Intel, proposed that the number of transistors per chip will double every year [11]. In 1975 he revised this estimation for proposing a redoubling of transistors per chip approximately every two years. This forecast has been followed by the industry for almost 50 years now. However, the scaling of transistors has a natural limit set by the atomic dimensions. The International Technology Roadmap of Semiconductors (ITRS) [12], which sets development standards and outlines future developments, published its final roadmap in 2016, because the classical scaling approach would reach its ultimate limits in the 2020s [13]. Thus, in 2016 the IEEE International Roadmap for Devices and Systems (IRDS) [14] was founded which is the successor of the ITRS and which has a broader focus on future developments. One of the newly defined key topics is *Cryogenic Electronics and Quantum Information*, which discusses the role of quantum computing as a new emerging field.

## **1.2 Cryo-CMOS Applications**

As *Moore's law* reaches its limits with respect to scaling the transistors on the chips, it is necessary to develop *Beyond CMOS* technologies [14]. *Beyond CMOS* as it is defined by the IRDS spans a wide range of research fields, such as carbon nanotube FETs, graphene based devices, molecular electronics, spintronics, optical computing, or superconducting computing [14]. The most prominent application of the latter, is superconducting quantum computing. Various approaches for building a quantum computer (including the superconducting approach) need cryogenic environments, which have made cryo-CMOS an emerging field in the past years. However, cryo-CMOS has also multiple other potential applications, such as high-performance computing [15–17] or space technologies [18]. Quantum computing (QC) and high-performance computing (HPC) will be introduced in more detail in the following, because these are central cryo-CMOS applications in the *Beyond CMOS* program of TU Vienna's research partner *imec*.

#### 1.2.1 Quantum Computing

With the *First Quantum Revolution* in the early 20<sup>th</sup> century, a range of technologies which determine our daily lives nowadays emerged. Electronics, satellites, lasers, medical imagery, etc. would not have been realizable without a deep understanding of quantum mechanics. Now, for the *Second Quantum Revolution*, global players invest billions for research and development of new technologies. In its 14<sup>th</sup> 5-Year-Plan for 2021 to 2025, China declared quantum technologies as a key technology [19]. Within the *Quantum Flagship* project started in 2018 [20], the European Union invests at least 1 Billion Euros in the research on quantum technologies with the ultimate goal of developing a quantum computer (QC) that is able to outperform classical computers in certain tasks. But not only governments invest Billions into QC, also private technology companies see a potential market and already demonstrated a QC on small scales, e.g. Sycamore from Google [21], IBM Q [22] or Quantum Inspire from Intel/QuTech [23]. An overview of the largest QC projects is given in Fig. 1.1.

**Figure 1.1.** First proof of concepts for QC were shown around the turn of the millennium [24–27]. Different approaches are under development for universal quantum computers (UQC): Superconducting qubits: IBM [28], Rigetti [29, 30], Intel [31], Alibaba [32], MISIS [33], Transmon qubits: Goolge [21, 34, 35], Rigetti (Project Acorn) [36], Electron spin qubits: QuTech/TU Delft [23, 37, 38], Trapped Ions: IonQ [39, 40], Honeywell [41–43], Photonics: Xanadu [44, 45], USTC [46, 47]. Quantum annealing systems, which are not UQC, are commercially available since 2011 [48–51]. The goal announced by Intel and Google is a UQC with 1 million physical qubits by 2030.

While classical computers can solve problems from the complexity class BPP (bounded-error probabilistic polynomial time) with efficient probabilistic algorithms, QCs can access the complexity class BQP (bounded-error quantum polynomial time) and can thus solve certain problems very efficiently, which are not accessible for classi-

cal computers within a reasonable computation time [52]. This class of BQP problems occurs in various fields such as cryptography [53], machine learning [54], medicine [55], computational chemistry [56] or in the financial sector [57], and thus attracts a large interest from different stakeholders in industry and research alike.

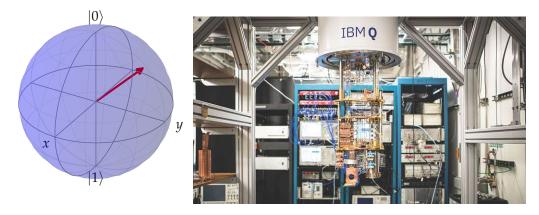

QCs are based on the fundamental concept of quantum bits (so called *qubits*), the basic units in quantum information technology, which are analogous concepts to binary bits, which are well known from classical computers. Mathematically, a qubit is a linear combination (superposition)  $\alpha |0\rangle + \beta |1\rangle$  of two orthogonal basis vectors  $|0\rangle$  and  $|1\rangle$ . This superposition is typically represented by a Bloch sphere, as can be seen in Fig. 1.2 (left). By using qubits, it is possible to build quantum logic gates, the basis of quantum circuits [52]. A single-qubit gate operation can be represented by a  $2 \times 2$  unitary matrix having the effect of a rotation of the Bloch vector on the spherical surface. While the mathematical description of single qubits is rather simple, the engineering task of building physical qubits is still extremely challenging. Since qubits use fundamental properties of quantum mechanics, such as superposition and entanglement, they also suffer from decoherence. Decoherence can be interpreted as an irreversible information loss of quantum states as soon as there is any type of interaction with the environment. To minimize this interaction, qubits are operated at cryogenic temperatures. Despite the many difficulties for the operation of qubits, there have been first major successes. The QCs of Google, IBM, and Intel/QuTech operate between 50 and 100 qubits and successfully run some simple quantum algorithms [21-23]. In 2019 Google even announced that they reached quantum supremacy. They claimed that it would take their quantum processor Sycamore with 54 qubits (53 functional ones) about 200 seconds to sample one instance of a quantum circuit one million times, a task for which a state-of-the-art supercomputer would need around 10,000 years [21]. However, this claim turned out be be rather controversial, because IBM published on their research blog that the task could also be done in 2.5 days on a classical computer with a far greater fidelity [58]. Independent of whether quantum supremacy has already been reached or not, the whole discussion addresses a problem which is highly artificial and currently not relevant for real-world applications. To run more useful algorithms like Shor's algorithm for prime factorization [53] or Grover's algorithm for searching an unordered list [59], it is necessary to operate thousands or millions of qubits. To enable this, there is a multitude of challenges which still need to be overcome.

One of the most important ones is the choice of the physical qubits. In theory, any two-state quantum system could be considered as a basis, however, no leading qubit technology has been established withing the QC community yet. Therefore, many different technologies are currently explored, for example trapped ion qubits [61], qubits based on crystal impurities [62, 63] or single photons [64]. The qubittechnologies used by the big tech-companies are superconducting qubits [21, 28] and silicon qubits [23, 37]. These technologies have been demonstrated already on small

**Figure 1.2.** Left: Mathematical representation of a qubit as Bloch sphere, which represents all possible states as superposition of  $\alpha |0\rangle + \beta |1\rangle$ . Operations on a qubit are represented by unitary matrices, resulting in a rotation of the vector on the sphere. Right: Quantum computer from the *IBM Q* project. The golden chandelier in the photograph shows different stages, from the mK-stage at the bottom to room temperature at the top. Figure taken from [60].

scales and they can be produced in industrial cleanrooms for 300mm wafers [65–67]. For these reasons, they are currently also in the focus of our research partner *imec* [67].

#### **Superconducting Qubits**

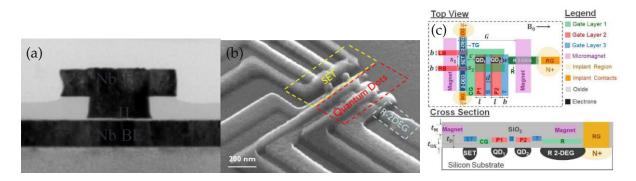

Among all qubit technologies, the superconducting qubit approach is currently the most advanced one in terms of the number of qubits, as can be seen in Fig. 1.1. Here, the qubits are based on Josephson Junctions (JJs), see Fig. 1.3 (a). Typically, JJs consist of two superconducting stripes, which are connected via a tunnel oxide in between. At deep-cryogenic temperatures (in the mK-regime) JJs act as non-linear inductors [68]. While a linear inductor in an LC-circuit would lead to equidistant energy levels in the corresponding quantum harmonic oscillator, the anharmonicity of a non-linear JJ leads to non-equidistant energy levels. This allows to take the ground state  $|0\rangle$  and the first excited state  $|1\rangle$  as two-state quantum system without allowing a higher state to become accessed. The manipulation of the qubit (which is the rotation on the Bloch sphere) can be induced by microwave pulses sent to an antenna which is coupled to the qubit. The frequency of this wave determines the rotation between the different energy levels. It has to be noted that there are various realizations of superconducting qubits based on non-linear inductors operating at cryogenic temperatures. A more detailed overview which realizations exist and how superconducting qubits work can be found in [68–71].

#### **Electron Spin Qubits**

Another class of qubits are silicon spin qubits, which is a collective name for various technologies, based upon using the spin of a charge carrier as two-state quantum system. There are various types of spin qubits, e.g. based on Si/SiGe [74], Si SOI [75], or based on Si MOS [76]. The latter ones are also in the focus of our research partner

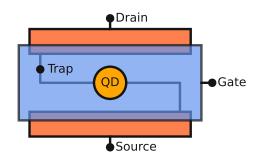

**Figure 1.3. (a)** Cross-section transmission electron microscope (TEM) of a fully patterned Josephson junction. **(b)** The scanning electron microscope (SEM) image of a Si electron spin qubit shows a single electron transistor (SET) for readout, two quantum dots (QDs) at the Si/SiO<sub>2</sub> interface, and the 2-dimensional electron gas reservoir for loading the QDs. **(c)** The schematic of a silicon spin qubit shows multiple gates for the qubit confinement and two magnets for operating the qubits. Figures taken from [67, 72, 73].

imec [65, 67, 73, 77] and are therefore discussed in more detail in the following. A SEM image of the qubit can be seen in Fig. 1.3 (b), where the single electron transistor (SET), the two quantum dots and the 2-dimensional electron gas (2-DEG) are highlighted. Several gates are needed to electrostatically confine the two quantum dots QD<sub>1</sub> and QD<sub>2</sub> located at the Si/SiO<sub>2</sub>-interface as can be seen in Fig. 1.3 (c). The 2-DEG serves as a charge reservoir enabling the loading of the QDs. The qubits can then be manipulated with a magnetic field created by micromagnets via electric dipole spin resonance [78] (alternatively, electron spin resonance can be used). Using the SET it is possible to readout the spin states using spin-charge conversion [73, 79]. A series of qubit operations using the magnetic field allows then the execution of quantum algorithms. Unlike superconducting qubits, the fabrication of Si spin qubits could benefit from many advantages of modern CMOS scaling which makes the concept highly interesting for commercial applications [65]. In theory, silicon spin qubits are ideal candidates for a cointegration of CMOS control hardware and qubits on the same chip [76]. However, state of the art projects are dominated by superconducting qubits (see Fig. 1.1) while spin qubits lag behind. The main reason for this is the limiting gate fidelity which describes how close two realized quantum states are. The fidelity of spin qubits is below the threshold required for complex quantum algorithms which leads to error rates of gate operations around 1% and thus makes the up-scaling impossible [65]. One of the main limitations for fidelity is the non-uniformity of qubits, which arises from the fabrication process. Among other processes, interface defects between the Si and the SiO<sub>2</sub> layer can be introduced during manufacturing, which has the consequence that every QD behaves slightly different and it is thus necessary to find for every qubit the right operation voltage regime individually [80]. Here, knowledge from the semiconductor industry, specially from the field of device reliability, can be used to improve the interface quality and to further specify the limiting factors.

#### **Classical Control Interface**

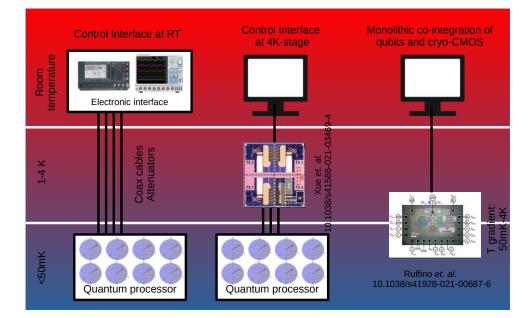

**Figure 1.4.** The first successful QCs use a dilution refrigerator for bringing the quantum processor to the sub-K regime. The qubits are controlled via coaxial cables with electronics at RT. Since this leads to a wiring bottleneck, lots of effort has been spent to design cryo-CMOS control interfaces working at the 4 K-stage [81]. Recently, first successes have been published bringing a monolithic co-integration of qubits and the cryo-CMOS control hardware to the cryogenic stage, where a large temperature gradient between the qubit layer at 50 mK and the control layer at 1 K to 3 K occurs [82, 83].

While the importance of the choice of the qubit technology is crucial, another less obvious bottle neck appears at the classical control interface for qubits. Until recently, existing QCs with a maximum of  $\sim$ 100 qubits have used racks full of electronic equipment (RF sources, DC sources, etc.) at room-temperature, where each individual qubit is connected via several coaxial cables to electronic instruments [81]. For such small systems, fidelities of above 99% can already be reached [84, 85]. However, for QCs which should be able to solve real-world applications the operation of thousands or millions of physical qubits is necessary to perform calculations together with quantumerror correction schemes, such as surface codes [86, 87]. For such large-scale QCs the research approach of room-temperature electronics fails for multiple reasons. The signal integrity across the RF lines for controlling the qubits gets too low, the number of possible physical connections at the test chip is limited, and the damping by the high resistivity of the vacuum throughputs becomes too high. Therefore, the classical control interface must be integrated within the cryostat and located as close as possible to the quantum processor. For this, CMOS technology is an ideal candidate for the control interface, because it can be produced in a high-quality commercially, allows the integration of billions of transistors, has a low power consumption and is functional even in the sub-Kelvin regime [88–92]. However, to avoid heat transfer to the qubits, the power budget of the control interface is extremely limited to approximately 1 W at the 4-K stage and to less than 10 µW at the mK stage [89, 93]. Additionally, noise leads to decoherence which reduces the qubit fidelity [78]. With these given restrictions near-quantum-limit amplifiers [94–96], ultralow-loss resonators [97, 98], circulators [99], multiplexers [100], cryogenic filters [101], wirebonds [102], DAC/ADCs [103–105], and many more components have been developed to realize cryogenic circuits. These building blocks have recently enabled the design of fully-fledged cryo-CMOS controllers for qubits, located at the 4-K stage [81, 92, 106]. This is an important intermediate step which not only allows to drastically reduce wiring but is also an important step towards fully integrated control electronics and qubits enabling up-scaling, as can be seen in Fig. 1.4. Recently, a first proof-of-concept of a monolithically integrated quantum–classical hybrid circuit was realized [82, 83]. This approach of unifying spin qubits in Si quantum dots and CMOS circuit technology could have the potential of using very large-scale integration (VLSI) and the experience collected over decades in the semiconductor industry for the production of monolithical qubits.

#### **1.2.2 High Performance Computing**

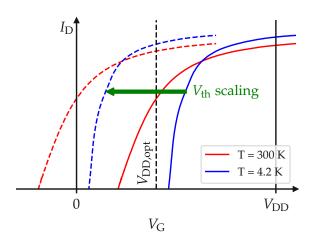

Another potential application for cryo-CMOS application-specific integrated circuits (ASICs) is the field of high performance computing. The changes in the  $I_D(V_G)$  characteristics of the transistors which are the core of the ASICs towards cryogenic temperatures, can be deliberately used to increase logic switching speed or to decrease the supply voltage  $V_{DD}$ , which allows a reduction of the total energy consumption [15–17]. Fig. 1.5 shows qualitatively how the  $I_D(V_G)$  curve of a MOSFET changes between room temperature and 4.2 K. At cryogenic temperatures, phonon scattering becomes reduced which leads to a higher charge carrier mobility, and as a consequence to an increasing on-state current  $I_{ON}$ . Also the subthreshold slope gets steeper leading to an increasing transconductance  $g_m$ . Additionally, the threshold voltage  $V_{th}$  increases due to the shifting semiconductor Fermi level and the temperature dependent band gap widening. A detailed discussion of these properties including certain saturation effects is given in Section 6.

While at room temperature  $V_{\text{DD}}$  can not be scaled down due to the constraining  $V_{\text{th}}$  and a large *SS* which would result in a significant off-state current, the steep transition at cryogenic temperatures opens new possibilities. For instance, a scaling of  $V_{\text{th}}$  allows an operation at considerably lower  $V_{\text{DD}}$ , as indicated in Fig. 1.5 [16]. There are multiple approaches for achieving the  $V_{\text{th}}$  scaling, e.g. it is possible to optimize the gate metal by choosing a metal with a band edge work function which meets  $V_{\text{th}}$  at the reduced target [15]. Additionally, lower band gap channel materials such as SiGe or Ge can be used to reduce  $V_{\text{th}}$  [15]. Another approach aims for using metal-oxide cap induced interfacial dipole layers [15] to optimize  $V_{\text{th}}$ . Overall, a device with an optimized  $V_{\text{th}}$  operating at cryogenic temperatures allowing a low- $V_{\text{DD}}$  operation has

**Figure 1.5.** The temperature dependence of the charge carrier mobility, the Fermi level, the band gap widening and other MOSFET parameters affects the  $I_D(V_G)$  transition curve. Towards cryogenic temperatures the  $I_D(V_G)$  curve gets steeper and the on-state current increases. This can be used in combination with threshold voltage  $V_{th}$  scaling to decrease the supply voltage  $V_{DD}$  which allows to increase the logic switching rate and to reduce total power consumption [15].

the potential of a significant higher logic switching rate. Chiang *et al.* proposed for an advanced FinFET technology a speed increase of around 50% when operating at 77 K with a constant operating power [15]. For a planar 28 nm high- $\kappa$  metal gate technology, Saligram *et al.* claimed a 90% performance/Watt improvement while operating at 6 K, however, in their calculation the cost of cooling has not been included [107]. But even with including the power of the needed refrigeration, a net power reduction of approximately 30% can be achieved [15].

Next to  $V_{\text{th}}$  scaling, the operation of MOSFETs at a very low- $V_{\text{DD}}$  leads to additional reliability challenges which have to be considered for circuit design for cryo-CMOS applications. With the lowering of  $V_{\text{DD}}$  the margins for  $V_{\text{th}}$  and *SS* also become more narrow meaning that the variability in the transfer curve must be minimized to guarantee a reliable logical switching. Furthermore, reliability issues such as bias temperature instability (BTI) and random telegraph noise (RTN), which are introduced in the upcoming section, must be reduced to a minimum, because low- $V_{\text{DD}}$  applications do not leave room for large threshold voltage shifts [108].

## 1.3 Reliability and Variability Issues in Cryo-CMOS

By operating devices at cryogenic temperatures, new challenges for CMOS engineering arise. Performance and device characteristics are strongly affected by the operation temperature and models developed for room temperature and above considerably loose in accuracy at low temperatures. Therefore, a large effort was put into the development of cryogenic models for transfer characteristics [109] and derived quantities as subthreshold swing [110], threshold voltage [111], on-state current [112], etc. While the proposed models steadily improve, reliability issues are rarely addressed. However, the stable operation can be affected by a wide range of stress mechanisms, for example caused by radiation, heat, mechanical or electrical stress. These diverse stress mechanisms can have an impact on the transfer characteristics by reducing the performance, increasing leakage currents, or leading in the worst case to a complete oxide breakdown.

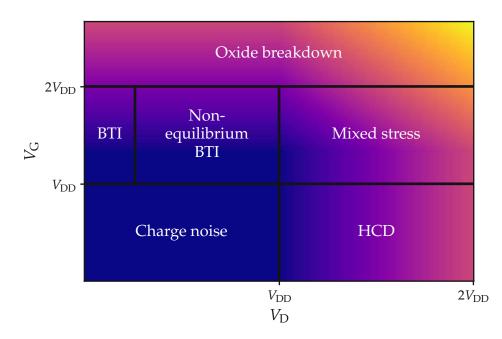

**Figure 1.6.** A schematic representation of the  $\{V_G, V_D\}$ -space shows the dominating degradation mechanisms for the different bias regimes.

Device aging is inevitable during regular operation, thus, a highly stable dielectric layer is an important building stone for meeting the lifetime-criterion of electronic circuits. Therefore, the focus of this work will lie on aging mechanisms caused by electrical stress, and the impact of this stress on pre-existing or generated defects in the MOSFET oxide. These defects can capture and emit a charge and thus affect the transfer characteristic of devices. Oxide defects and defects at the interface between oxide and substrate can not only occur in transistors, they can also disturb the stable operation of quantum dots. As discussed in the previous section, QDs are complex structures with multiple oxide layers. Since reaching a high fidelity is one of the main challenges in the engineering of qubits, guaranteeing high quality interfaces between substrate and these oxide layers is essential to avoid charge trapping.

For understanding the mechanisms of charge trapping, it is necessary to differentiate between various degradation mechanisms, which will be dominant at different bias conditions as can be seen in Fig. 1.6

• **Bias temperature instability (BTI)**: BTI occurs, whenever a bias is applied on the gate side of a transistor. The applied bias reduces the barrier between the

charge reservoir, which can be either the channel or the gate, allowing the traps to capture charge. The trapped charges then affect the electrostatics and consequently change the device transfer characteristics. On large-area devices, this can be seen as a continuous shift of the threshold voltage, caused by thousands of defects capturing and emitting charges simultaneously when the threshold voltage is monitored over time. By scaling the geometry of a transistor, discrete steps can be seen in the measured current, which reveal single charge capture and emission events. To examine this effects, typically elevated temperatures and voltages above the operational condition are used to accelerate the degradation. Since elevated temperatures do not make sense for the study of BTI in cryogenic environments, studies in this work will often be based on elevated voltage conditions. Also, it has to be noted that generally BTI is classified into negative BTI (NBTI) and positive BTI (pBTI), determined by the sign of the gate voltage applied during the stress, which can be measured on both nMOS and pMOS. However, typically the focus lies on NBTI on pMOS devices and PBTI on nMOS devices corresponding to the typically used bias conditions. A more detailed introduction to BTI can be found in Section 8 and in [113–115].

- 1/f noise and random telegraph noise (RTN): Oxide defects can exchange charges with the device substrate or the gate, even under non-accelerated conditions. The ongoing mechanisms are the same as in BTI, i.e. defects can capture and emit charges, altering the device electrostatics and leading to fluctuations in the device parameters. However, in contrast to BTI, less defects can contribute to the noise. But similar to BTI, while on large-area devices the fluctuations are continuous and known as 1/f noise, there are discrete steps on scaled devices, which are known as random telegraph noise (RTN) [116–118].

- Hot carrier degradation (HCD): Compared to BTI which focuses on elevated gate insulator fields while no drain-source bias is applied to result in a uniform carrier distribution along the channel during stress, HCD describes the degradation under non-equilibrium conditions, i.e. at accelerated drain bias conditions. A high drain-source field accelerates the carriers to either drain or source (depending on the carrier type) leading to carriers with a high kinetic energy. These so-called *hot carriers* cause damage in the channel or at the Si/SiO<sub>2</sub> interface where they can create interface defects which can capture and emit charges. However, unlike BTI, the damage caused by the high energetic carriers is mostly irreversible. A more detailed overview to HCD can be found in [119, 120].

The above mentioned degradation mechanisms have been well studied over the past decades and a profound knowledge has been gained on how the behavior of MOSFETs is affected in various ways. In addition, the community of defect physics has made lots of progress in understanding the role of defects in MOSFET degradation, and fundamental theories like nonradiative multiphonon (NMP) theory have been established to describe

the interaction of defects with charge reservoirs, as will be discussed in detail in Section 3. While there are innumerable reliability studies on reliability issues in electronics in above room-temperature environments, there is a lack of degradation studies in cryogenic environments. However, with the ever increasing interest in QC the research for robust electronic systems operated in cryogenic environments becomes increasingly important. As one part of it, the gained knowledge from defect studies at cryogenic temperatures helps developing devices operating stably in such environments. This is of special importance, because many cryogenic applications are extremely sensitive to reliability issues. As discussed, the classical control interface of quantum computing should be as close as possible to the qubits and thus at the cryogenic stage. At the same time, qubits are extremely noise sensitive, therefore charge noise must be reduced as much as possible in the CMOS control unit is as close as possible to the qubits. Here, charge noise is very likely to accelerate dephasing of the qubits and can therefore have a negative impact on the qubit fidelity.

Reliability issues play a crucial role in high performance computing. A low- $V_{DD}$  is important for electronics in HPC to increase the logical switching rate and to decrease the total power consumption. However, it comes with the price that circuits become very sensitive to variability. A large variability of the devices has the effect that a switching between on- and off-state can not be guaranteed anymore within low- $V_{DD}$  applications. Additionally, small  $\Delta V_{th}$  shifts can already disturb the stable switching and thus compromise a reliable operation. Therefore, it is essential to include variability and reliability considerations in design of optimized CMOS applications [121].

Knowledge on defect physics gained from reliability studies on cryo-CMOS applications can be further used in related fields. Since cryogenic environments are often used to reduce noise, charge noise caused by oxide defects or by interface defects between the numerous different processed layers (see Fig. 1.3 (c)) is a major concern for qubits. In the qubit design, one of the main engineering challenges is reaching a high fidelity and avoiding decoherence. Defects which get created during device manufacturing can affect the readout of the spin in superconducting qubits [122–125] or have an impact on the confinement of the QD forming the electron spin qubits causing dephasing [78, 80, 126–132]. Therefore, understanding the physics of the occurring traps from theoretical calculations [133–135] and from experiments as shown in this work can deliver a valuable contribution in reducing the loss of decoherence in solid state qubits.

## 1.4 Scope and Outline of this Work

In this work, two approaches for developing a better understanding of MOSFET reliability at croygenic temperatures are followed. A theoretical, modeling approach presented in Part I *Modeling and Simulation of Defects*, in which an efficient charge trapping model for cryogenic temperatures is developed. In Part II *Defect Characterization at*

*Cryogenic Temperatures,* various characterization, reliability and variability studies on multiple technologies are presented and analyzed with the models from Part I.

#### Part I – Modeling and Simulation of Defects

#### • Chapter 2 – Defect Candidates

This chapter reviews specific defect candidates which have been found to play a major role in device degradation during operation. The defect candidates for SiO<sub>2</sub>, SiON and HfO<sub>2</sub> insulators have been studied in detail with theoretical tools such as density functional theory (DFT) or technology computer-aided design (TCAD), as well as experimentally. This allows the calculation and verification of various trap properties like densities, trap levels, relaxation energies or their typical spatial positions.

#### • Chapter 3 – Charge Transfer Models

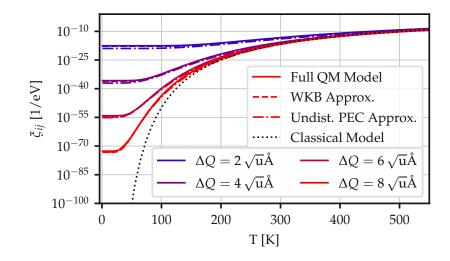

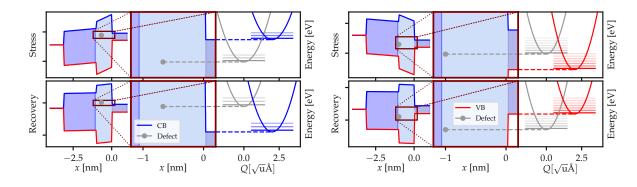

Charge trapping in oxides is a stochastic process which describes the exchange of charge carriers between a trap and a reservoir. A mathematical description of this trapping and detrapping process is essential for reliability studies. First models developed in the 1950s have been steadily improved for allowing precise simulations of measurements. In this work, the 2-state nonradiative multiphonon (NMP) models is used. This model is valid even in the limit of cryogenic temperatures, however, it is computationally expensive and thus not suitable for reliability simulations. Therefore, an efficient WKB-based charge transition model is derived in this work. This model is numerically superior and gives very precise results compared to the full model. An even more efficient model is presented, which is based on the assumption of non-deforming potential energy surfaces during charge transitions.

#### • Chapter 4 – Reliability Simulations

The charge transition models presented in Chapter 3 are now used for reliability simulations. For this, the WKB-based approximation of the 2-state NMP model was implemented in the device reliability simulator *Comphy*. *Comphy* uses a surface potential based 1-dimensional electrostatics. By sampling thousands of defects in the oxide, the electrical response of these defects after applying a gate voltage allows to compute the caused threshold voltage shift. These simulations are used to compare the theoretical studies with measurements.

## Part II – Defect Characterization at Cryogenic Temperatures

• Chapter 5 – Measurement Setup and Technologies

Two different measurement setups have been used within this work to characterize

various MOSFET technologies. On cryogenic probe stations, electrical measurements between 4.2 K and room temperature have been conducted using a Helium cooling system. Manual probe arms allowed the characterization of large-area planar high- $\kappa$ -metal gate devices, planar SiON devices and planar MoS<sub>2</sub> devices. Since manual probing is a very time-consuming task and only a handful of devices can be characterized at once, a different approach was chosen to obtain statistical data representative for a certain technology. *SmartArrays* with thousands of transistors which can be addressed digitally have been characterized. This allows collecting large data sets and enables the study of different designs at cryogenic temperatures. In this work, time-zero variability and mismatch and their dependence on temperature and device geometry have been studied, which can be very critical especially for low- $V_{DD}$  applications.

#### • Chapter 6 – Time-Zero Characterization

Time-zero studies form the foundation for every reliability study. The conduction of  $I_D(V_G)$  curves allows the analysis of various MOSFET parameters such as threshold voltage, subthreshold swing or on-state current and their temperature dependence. The modeling of the temperature dependence of these parameters is extremely complex and must not only include the shifting Fermi level, the changing Fermi-Dirac statistics or bandgap widening but also interface and band-edge states. Time-zero characterization on *SmartArrays* allows studying the variability and the mismatch of the extracted parameters and their temperature dependence.

#### • Chapter 7 – Charge Noise Characterization

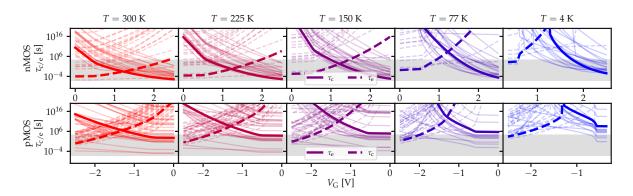

Cryogenic environments are often used to minimize noise in the measurements. Thus, it is extremely important to understand the impact of low frequency noise (1/f noise) caused by traps at cryogenic temperatures. For this, the temperature and gate voltage dependence of RTN in various technologies has been studied. The findings have then be modeled with the quantum mechanical 2-state nonradiative multiphonon theory discussed in Chapter 3, which can correctly describe the temperature activation of charge trapping.

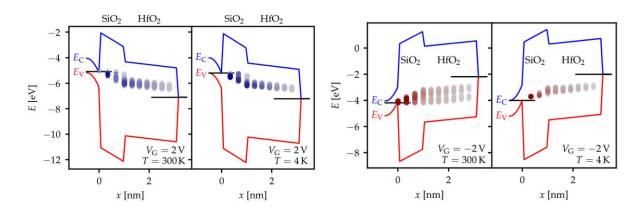

#### • Chapter 8 – Bias Temperature Instability

In this chapter BTI studies on various technologies are presented. The different freeze-out behavior of large area SiON and high- $\kappa$  metal-gate devices is discussed and modeled using the reliability simulator *Comphy*. For this, the quantum mechanical version of 2-state NMP theory has been used. Furthermore, BTI was studied on scaled MoS<sub>2</sub> devices using time-dependent defect spectroscopy (TDDS) measurements at cryogenic temperatures. Here, it is explicitly shown that single charge capture and emission events causing threshold voltage shifts are clearly visible at cryogenic temperatures.

# Part I

# Modeling and Simulation of Defects

# Chapter 2

## **Defect Candidates**

Reliability issues such as BTI, HCD, or charge noise, i.e. RTN, are caused by electrically active defects that can be located in the oxide or at its interface to the semiconductor bulk. These defects are introduced in the device during manufacturing, even in very optimized processes, or can be created during device operation at nominal bias conditions and temperatures and their formation can not be avoided. Since these defects typically have a negative impact on the device performance or, in the worst case, can even lead to the failure of the device, it is of major importance to understand how defects emerge and how they influence the device performance. Over the years, the manufacturing processes have considerably improved and as a consequence the number of active defects could be significantly reduced. Still, there are many applications which rely on an extremely low noise level and very narrow reliable operation conditions which is further motivation to investigate the physical processes involved in charge trapping. Since defects occur in a large variety, many different approaches are used for examinations, from theoretical tools such as DFT or TCAD, electrical examination tools as presented in Part II of this work, or physical characterization methods such as electron paramagnetic resonance (EPR) spectroscopy, X-ray photoelectron spectroscopy (XPS), or secondary ion mass spectroscopy (SIMS).

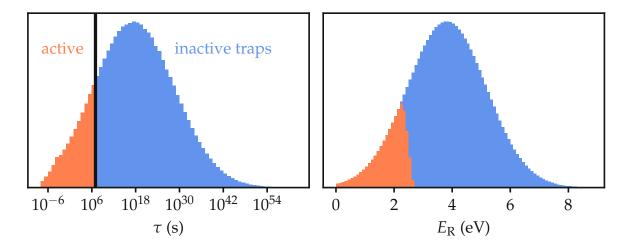

The combination of all these tools allows to search for specific defect candidates, which may play a major role in the device degradation during operation. The trapping properties of suitable defect candidates, such as relaxation energies, defect densities, trap level, and spatial position can be theoretically studied and linked to various experimental approaches using reliability simulations as presented in Chapter 4. The most important defect candidates for electrical reliability studies are introduced in the following sections.

### 2.1 Interface Defects

Silicon dioxide is the most common insulator in MOSFET technologies. During the fabrication of devices,  $SiO_2$  grows natively on silicon wavers when exposed to air via

oxidation, which makes it an ideal candidate as an insulator. The resulting thin layer (with a thickness below 1 nm) is called native SiO<sub>2</sub>. Alternatively, nitrited SiO<sub>2</sub> (SiON) is used as insulator to decrease the gate leakage current and to prevent dopants from diffusing from the channel into the insulator. The defect behavior in SiON insulators is similar to the one in pure SiO<sub>2</sub>, which typically allows using the simplified SiO<sub>2</sub> system in simulations [136].

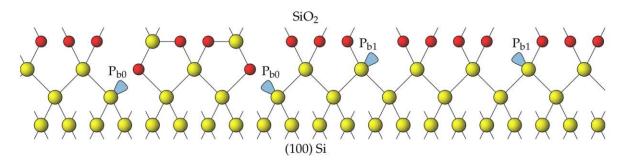

The lattice mismatch between the amorphous structure of the insulator layer and the semiconductor makes the presence of a certain amount of defects close to the interface inevitable. The interface defect density strongly depends on the combination of the materials used for the semiconductor and insulator and the processing conditions. Note that for Si/SiO<sub>2</sub> systems densities on the order  $10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> can be achieved [137]. For this material system, the best understood interface defect is the  $P_b$  center, which can appear on both, the (111) and the (100) oriented surface [138, 139]. In general, the  $P_b$  centers have been observed to occur in different chemical variations: The  $P_{b0}$  center of the form ( $\cdot$ Si $\equiv$ Si<sub>3</sub>) and the  $P_{b1}$  center, whose atomistic structure is not completely understood yet, are depicted in Fig. 2.1. Due to the unpaired electron at the Si side, the defects are also called *dangling bonds*.

**Figure 2.1.**  $P_b$  centers can occur in two chemical variations at the (100) oriented Si/SiO<sub>2</sub> interface: As  $P_{b0}$  center of the form ( $\cdot$ Si $\equiv$ Si<sub>3</sub>) and as  $P_{b1}$  center, whose atomistic structure is not completely understood yet. The unpaired *dangling bond* is shown represented by the bluish triangles. Figure reprinted from [140].

There are at least two trapbands corresponding to the  $P_b$  centers, one above and one below Si midgap, which allow electron capture and emission from and to the channel, respectively [141]. The trap levels of such interface defects lie within these trap bands, and they typically have small relaxation energies which leads to small relaxation times compared to bulk oxide defects [142]. Thus, the different relaxation energies can be used as an indicator which defects might be responsible for measured signals, as done e.g. in Section 7.4.

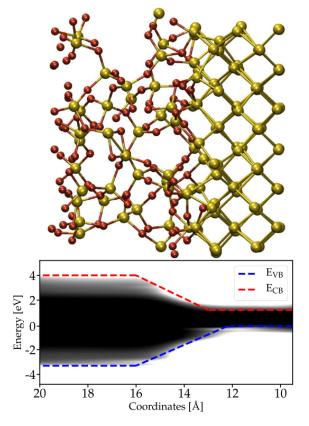

The oxidation of amorphous  $SiO_2$  on the Si substrate leads not only to interface defects but also to a continuous change in the density of states and the corresponding band edges [136], as shown in Fig. 2.2. This behavior can be explained by a gradual change in the ratio of silicon and oxygen atoms between bulk  $SiO_2$  and the Si substrate. The gradual change in the density of states and linear band edge structure has to be be

considered in device simulations, e.g. by correcting the WKB tunneling factors [136]. Fig. 2.2 shows the transition layer from amorphous bulk SiO<sub>2</sub> to the Si substrate which shows a thickness of 0.3 nm to 0.4 nm. This has the consequence that in high- $\kappa$  devices, which typically have a very thin SiO<sub>2</sub> layer of below 1 nm between the substrate and the high- $\kappa$  material, no bulk SiO<sub>2</sub> occurs.

**Figure 2.2.** The density of states does not change abruptly between amorphous bulk  $SiO_2$  and Si at the interface but is rather continuous. This can be explained by the continuously changing ratio of silicon (yellow spheres) and oxygen (red spheres) atoms from the Si substrate to bulk  $SiO_2$  and the influence of the Si surface. Figure taken from [136].

# 2.2 Bulk Oxide Defects

While in the early days of MOSFETs interface defects have been in the center of research, later also defects in the bulk oxide were added to a more complete description of device degradation.

# 2.2.1 Oxide Defects in Amorphous SiO<sub>2</sub> (a-SiO<sub>2</sub>)

Bulk SiO<sub>2</sub> is very well understood from both experimental characterization and theoretical studies. One intensively investigated defect candidate for a-SiO<sub>2</sub> is the *oxygen vacancy* (OV) [143–145]. It forms naturally during oxidation and is essentially a missing

O atom in a SiO<sub>2</sub> network (where an O atom ideally bonds with two neighbored Si atoms) which leads to a Si-Si bond. The defect is shown in the neutral (1) and positive (2) charge state in Fig. 2.3, whereby the prime ' denotes a metastable configuration which can be accessed via a thermal transition, as explained in Section 3.3. When the neutral OV traps a hole, the distance between the two Si atoms increases. As a consequence, the Si-Si bond can break, resulting in a Si dangling bond [146].

As shown in Fig. 2.3, the bond breaking and relaxation into a new stable configuration of the oxygen vacancy could be theoretically described by a 4-state model with the states 1, 1', 2', and 2. However, various first principle studies show that the energetic position of the defect inside the band structure of the insulator is too far below the valence band or too far above the conduction band of the Si substrate [147–149]. Therefore, oxygen vacancies are very unlikely to capture holes and stay neutral in pMOS transistors with relatively thin a-SiO<sub>2</sub> oxides and thus do most likely not contribute to BTI or RTN.

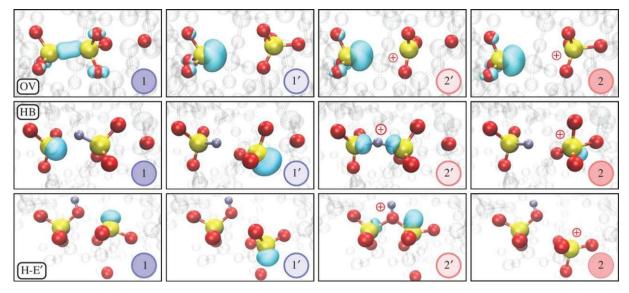

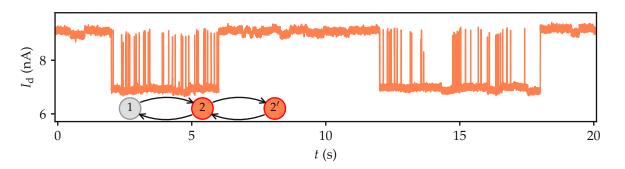

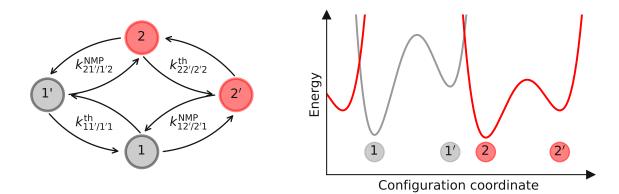

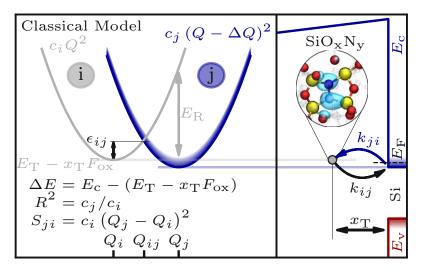

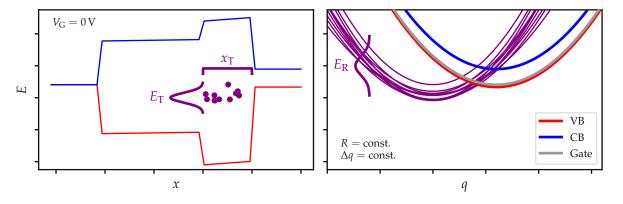

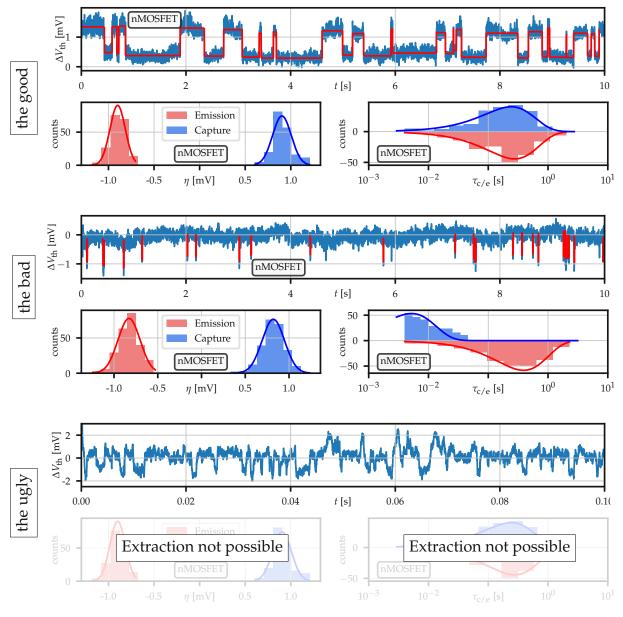

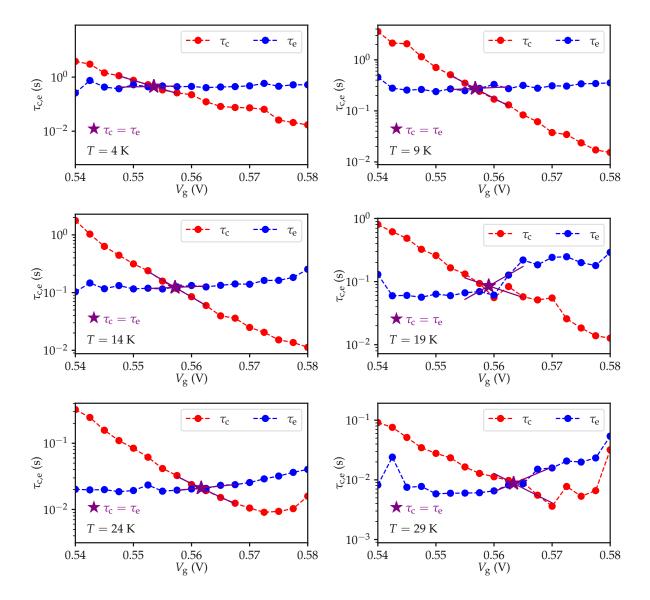

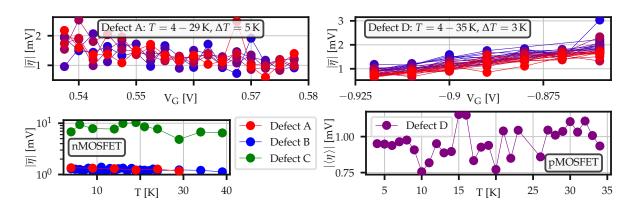

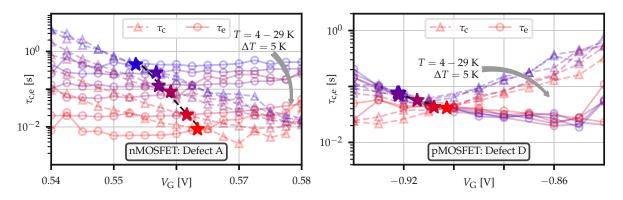

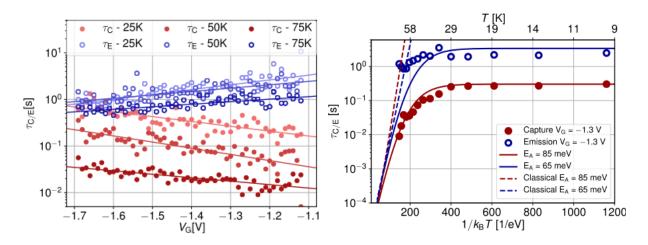

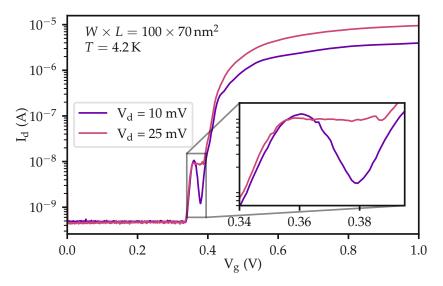

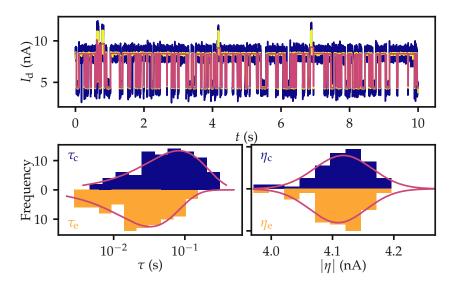

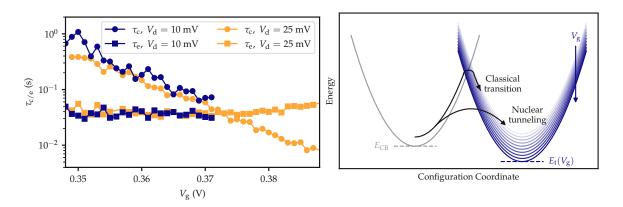

**Figure 2.3.** The atomistic configurations of the oxygen vacancy (OV), the hydrogen bridge (HB) and the hydroxyl-E' center (H-E') show that these defects can be described with a 4-state NMP model. The defects show two stable configurations 1 and 2 and can switch between theses stable states via the meta-stable states 1' and 2'. The turquoise bubbles show the highest occupied molecular orbital (HOMO) electron distributions. Figure reprinted with permission of the Royal Society from [149].