|

|

Biography

Hiwa Mahmoudi was born in Baneh, Kurdistan, Iran, in 1985. He studied electrical engineering at the K.N.Toosi University of Technology, Tehran, Iran (2003-2007), and received his MSc degree in Microelectronic Devices from the Sharif University of Technology in 2009. He joined the Institute for Microelectronics in 2011, where he completed his doctoral degree in 2014. His current scientific interests include Device Simulation in Spintronics and Microelectronics.

Stateful MRAM Arrays for Large-Scale Logic-in-Memory Applications

The scaling of Complementary Metal-Oxide-Semiconductor (CMOS) technology is facing fundamental physical and financial limitations. Standby power dissipation due to leakage has become a major challenge of today's CMOS Very-Large-Scale Integration (VLSI) circuits. Stateful logic provides zero-standby power for intrinsic non-volatile logic-in-memory designs and is a promising solution to overcome the leakage issue. A Spin-Transfer Torque (STT) Magnetic Tunnel Junction (MTJ) is a very favorable device for stateful logic as it inherently eliminates the state drift error accumulation, which is an important shortcoming in the TiO2-based stateful implication logic gates. We have demonstrated that by using STT-MTJ devices, stateful logic is realized via material implication (IMP) operation. A new improved STT-MTJ-based logic gate (Fig. 1a) is proposed. It significantly improves the performance of the implication logic as compared to conventional gate topology.

Because of the easy integration with CMOS, the MTJ-based logic gates are generalizable to STT-MRAM-based stateful logic architectures by using hybrid CMOS/MTJ technology. In a memory mode, the access transistors of one-transistor/one-MTJ (1T/1MTJ) cells act as on-off switches. In a logic mode, we use them not only as on-off switches, but also as voltage-controlled resistors to implement RG. Therefore, in the 1T/1MTJ-based implementation the structural asymmetry issue of the improved implication logic gates (Fig. 1b) is addressed. As a 1T/1MTJ cell is the basic element of the commercialized STT-operated Magnetoresistive Random-Access Memory (MRAM), the proposed implementation becomes generalizable to a stateful STT-MRAM logic architecture. The proposed STT-MRAM-based logic implementation enables non-volatile logic fan-out and provides high flexibility with regard to the use of arbitrary MTJs as input and output. The implementation is computationally complete, has a simple circuit structure (STT-MRAM), delocalizes computational execution, and eliminates the need for intermediate circuitry. It also enables parallel non-volatile computations and, therefore, is suited for complex logic functions evaluation and opens an alternative path towards zero-standby power logic systems, shifting away from the Von Neumann architecture by eliminating the need for data transfer between separate memory and logic units to shorten the interconnection delay.

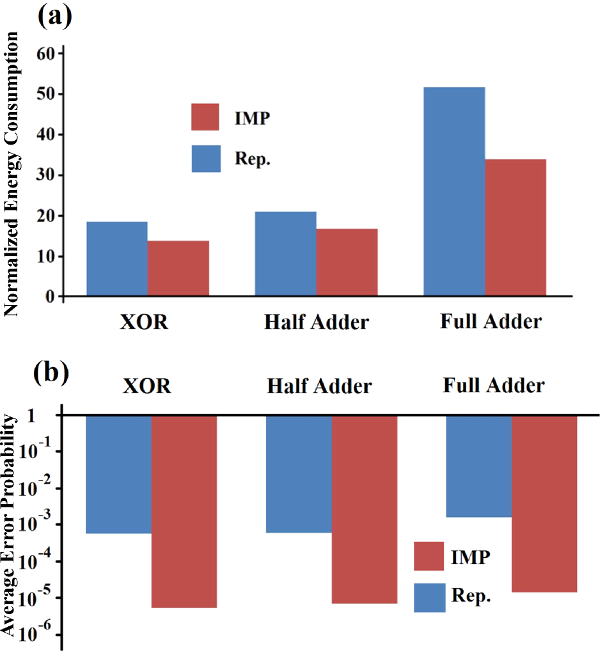

Reliability modeling and analysis is presented for optimizing and comparing 1T/1MTJ-based logic gates (Fig. 1b and Fig. 1d). It is shown that the proposed implication logic gate allows for the implementation of Boolean logic functions based on an up to now ignored propositional logic operation of material implication and significantly improves the reliability of the MTJ-based logic compared to similar circuits available from literature based on reprogrammable architecture, which realizes conventional Boolean logic operations, including AND, OR, NAND, and NOR operations (Fig. 1c). In order to compare the performance of the implication and the reprogrammable logic architectures, the energy consumptions and the average error probabilities of more complex Boolean functions, including an XOR, a half adder, and a full adder, are compared in Fig. 2. It illustrates that the implication logic architecture performs better with respect to the power consumption (Fig. 2a). Furthermore, Fig. 2b shows that the implication-based implementation of more complex functions exhibits about two orders of magnitude higher reliability than the most reliable design with the reprogrammable architecture.

Fig. 1: MTJ-based (a) implication and (c) reprogrammable logic gates. 1T/1MTJ-based realization of (b) implication and (d) reprogrammable logic gates.

Fig. 2: (a) Normalized energy consumption and (b) minimum average error probabilities plotted for different logic functions based on the implication (IMP)

and the reprogrammable (Rep.) logic gates. The energy is normalized by the TRUE operation switching energy which is equal to 18pJ for a pulse duration of t=50ns in the simulations.